# Programmable Logic

# Data Book

General Information

2

PAL Support

**Data Sheets**

**EPLD Development Systems**

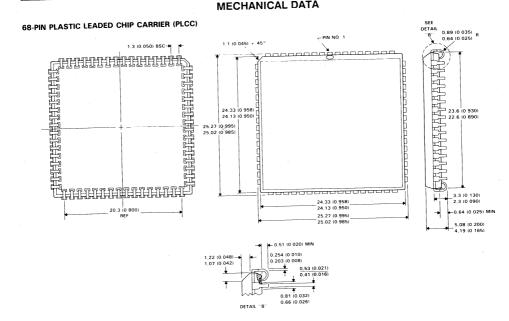

**Mechanical Data**

**F**9)

# The Programmable Logic Data Book

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1990, Texas Instruments Incorporated

#### INTRODUCTION

In this data book, Texas Instruments (TI) presents technical information on TI's broad line of programmable logic devices (PLDs), including the high-speed 5-ns PAL® circuits and high-density, low-power, Erasable Programmable Logic Devices (EPLDs). More than 40 PLD functions in industry standard architectures are available from Texas Instruments. For high-performance applications, TI also offers several high-speed programmable state machine devices. Where low power and reprogrammability are key considerations, TI offers its family of EPLDs. This data book includes specifications on existing and future products including:

- High-performance, low-power IMPACT<sup>TM</sup> and IMPACT-X<sup>TM</sup> 20- and 24-pin standard PAL<sup>®</sup> circuits including Tl's new 5-ns device

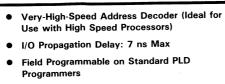

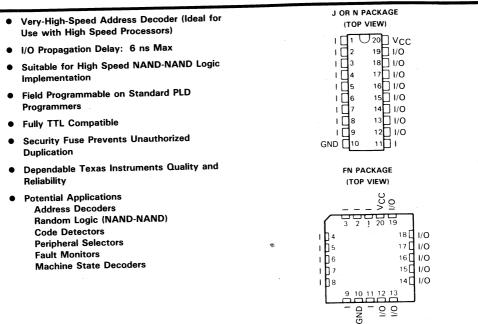

- Tl's high-speed 6-ns programmable address decoder, TIBPAD18N8-6

- Flexible, '22V10-architecture macrocell PAL® ICs including TI's enhanced version, the TIDPAL22V10-150BC

- Fast, programmable state machines, including enhanced versions of the 50-MHz '82S105B/167B and TI's complex TIBPLS506 with 58-MHz

- The TIBPSG507, programmable sequence generator with internal 6-bit counter and 58-MHz performance

- Speed improved versions of the industry standard EPLD architectures including the 20-ns EP630 and 15-ns EP330

Texas Instruments high-speed programmable bipolar devices utilize TI's advanced IMPACT<sup>TM</sup> and new IMPACT-X<sup>TM</sup> technologies. IMPACT-X<sup>TM</sup> uses trench isolation and polysilicon emitters to increase performance and reduce power dissipation compared to traditional processes. For EPLDs, TI utilizes its 1.0 micron high-voltage EPIC<sup>TM</sup> CMOS technology to combine the benefits of low power and higher speed.

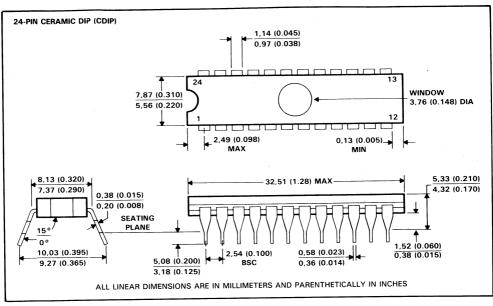

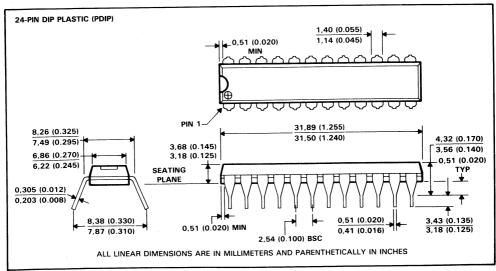

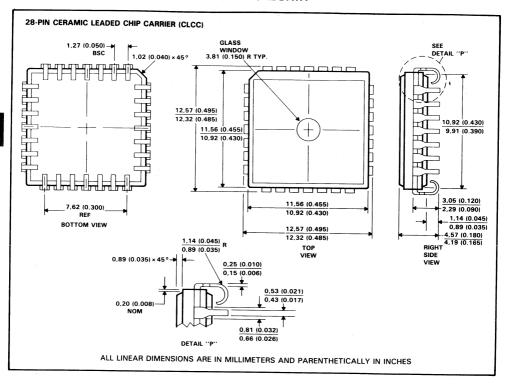

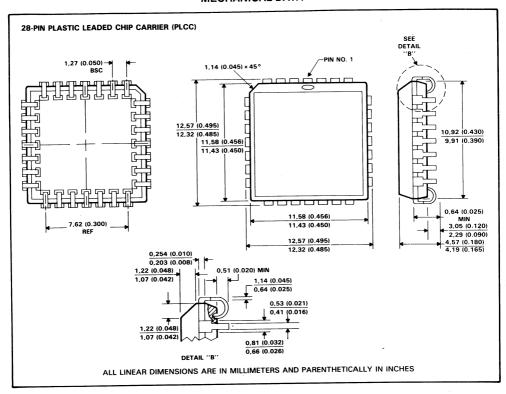

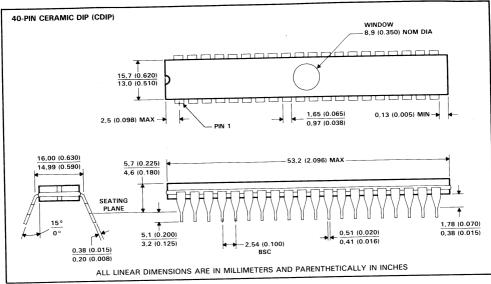

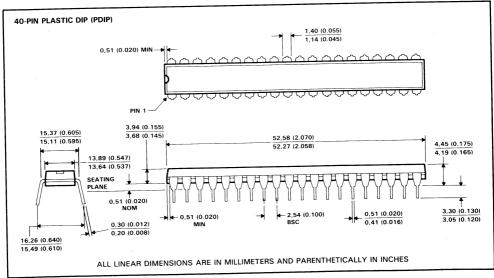

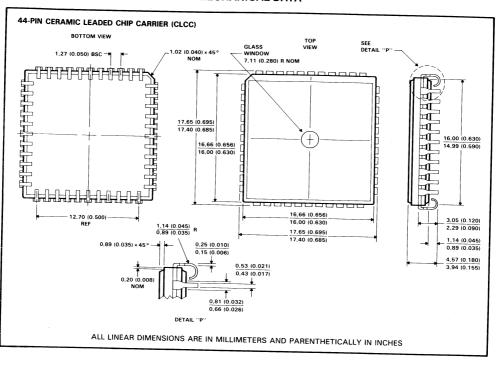

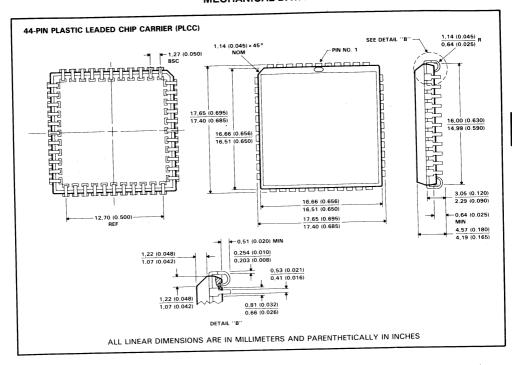

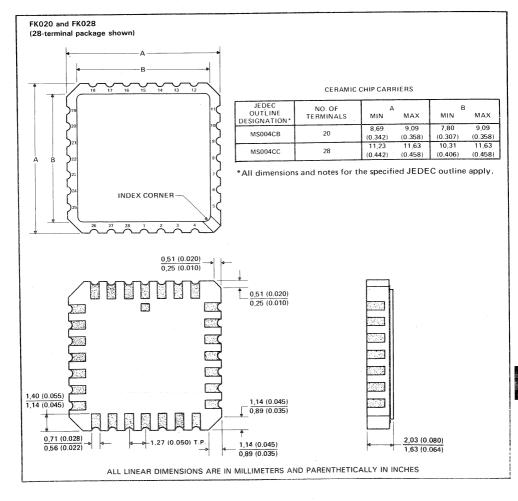

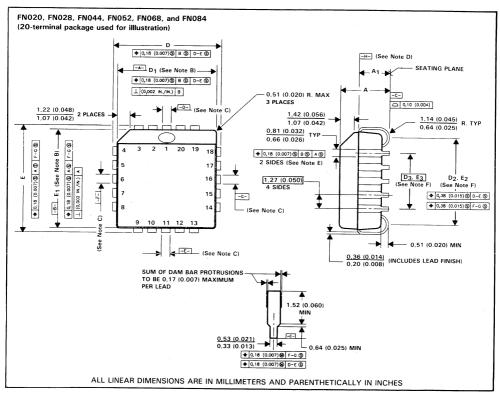

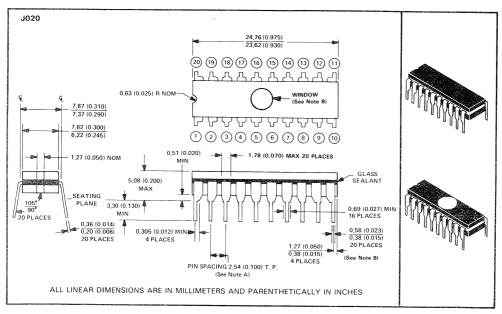

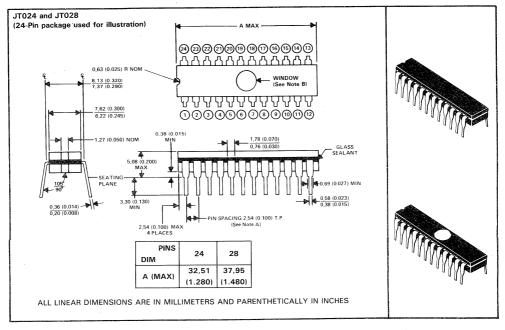

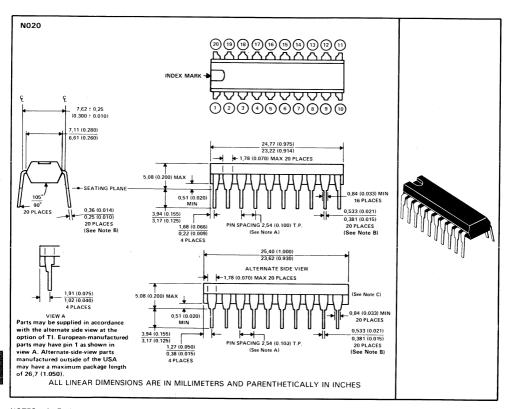

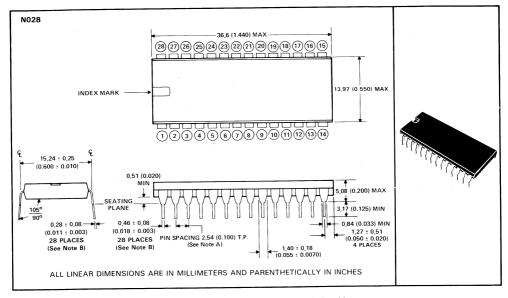

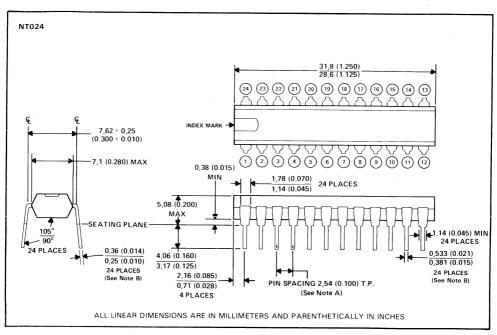

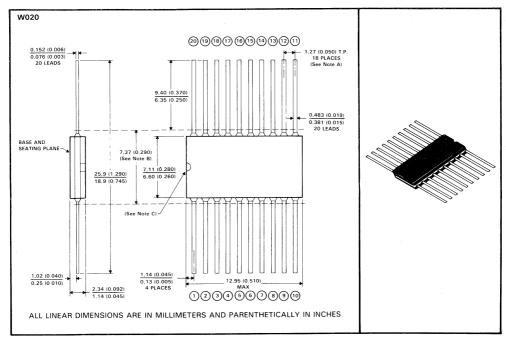

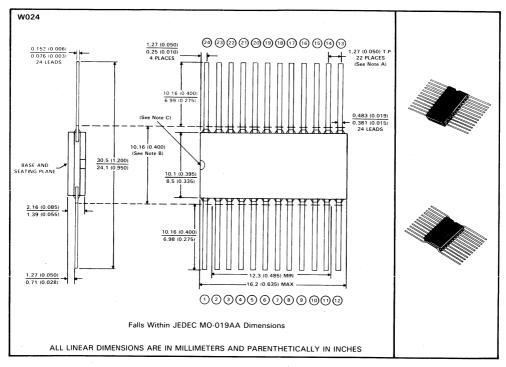

This volume contains design and specification data for 154 device types. Package dimensions are given in the Mechanical Data section in metric measurement (and parenthetically in inches). In some cases, package dimensions are included in the actual data sheet.

Several programmable logic application reports have been incorporated into this book to aid the design of TI PLDs. User notes also explain considerations for programming and testing of PLDs in a manufacturing environment.

Complete technical data for any Texas Instrument semiconductor product is available from your nearest TI field sales office, local authorized TI distributor, or by calling Texas Instruments at 49-8161-800.

PAL is a registered trademark of Monolithic Memories Inc. IMPACT, IMPACT-X, and EPIC are trademarks of Texas Instruments Incorporated.

| Gene  | ral Infori | matio | n      |      |

|-------|------------|-------|--------|------|

|       |            |       |        |      |

| Data  | Sheets     |       |        |      |

|       |            |       |        |      |

| PAL S | Support    |       |        |      |

|       |            |       |        |      |

| EPLD  | Develop    | oment | : Syst | tems |

|       |            |       |        |      |

**Mechanical Data**

# Contents

|                                 | Page |

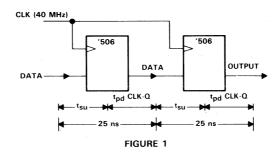

|---------------------------------|------|

| Alphanumeric Index              | 1-3  |

| Glossary                        |      |

| Explanation of Function Tables  |      |

| Ordering Information            |      |

| Hardware/Software Manufacturers |      |

| Third Party Design Centers      |      |

### **ALPHANUMERIC INDEX**

|                | Page                 |                    | Page                   |

|----------------|----------------------|--------------------|------------------------|

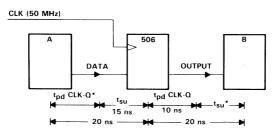

| EP330-15C      | EP330-25I 2-3        | TIBPAL16R8-5C      | TIBPAL16R8-7M 2-103    |

| LI 330-130     | EP330-25M 2-3        | TIBPAL16R8-7C      | TIBPAL16R8-10M 2-123   |

| EP610DC-25     | 2-15                 | TIBPAL16R8-10C     | TIBPAL16R8-12M 2-141   |

| EP610DC-30     | 2-15                 | TIBPAL16R8-12C     | TIBPAL16R8-15M 2-159   |

| EP610.IC-35    | 2-15                 | TIBPAL16R8-15C     | TIBPAL16R8-20M 2-173   |

| EP6101 C-25    | 2-15                 | TIBPAL16R8-25C     | TIBPAL16R8-30M 2-187   |

| EP610LC-30     | 2-15                 | TIBPAL20L8-5C      | TIBPAL20L8-7M 2-201    |

| EP610LC-35     | 2-15                 | TIBPAL20L8-7C      | TIBPAL20L8-10M 2-221   |

| EP610PC-25     | 2-15                 | TIBPAL20L8-10C     | TIBPAL20L8-12M 2-239   |

| EP610PC-30     | 2-15                 | TIBPAL20L8-15C     | TIBPAL20L8-20M 2-257   |

| EP610PC-35     | 2-15                 | TIBPAL20L8-25C     | 2-271                  |

| EP630-20 C     | EP630-25I 2-33       | TIBPAL20L8-15CNL . | 2-283                  |

| LI 030 20 0    | EP630-25M 2-33       | TIBPAL20L8-25CNL . | 2-283                  |

| EP910DC-30     | 2-47                 | TIBPAL20R4-5C      | TIBPAL20R4-7M 2-201    |

| EP910DC-35     | 2-47                 | TIBPAL20R4-7C      | TIBPAL20R4-10M 2-221   |

| EP910DC-40     | 2-47                 | TIBPAL20R4-10C     | TIBPAL20R4-12M 2-239   |

| EP010 IC-30    | 2-47                 | TIBPAL20R4-15C     | TIBPAL20R4-20M 2-257   |

| EP910 IC-35    | 2-47                 | TIBPAL20R4-25C     | 2-271                  |

|                |                      | TIBPAL20R4-15CNL   | 2-283                  |

|                | 2-47                 | TIBPAL20R4-25CNL   | 2-283                  |

| EP910LC-35     | 2-47                 | TIBPAL20R6-5C      | TIBPAL20R6-7M 2-201    |

| EP910LC-40     |                      | TIBPAL20R6-7C      | TIBPAL20R6-10M 2-221   |

| EP910PC-30     | 2-47                 | TIBPAL20R6-10C     | TIBPAL20R6-12M 2-239   |

| EP910PC-35     | 2-47                 | TIBPAL20R6-15C     | TIBPAL20R6-20M 2-257   |

| EP910PC-40     | 2-47                 |                    | 2-271                  |

| EP1810JC-35    | 2-65                 |                    | 2-283                  |

| EP1810JC-45    | 2-65                 | TIBPAL20R6-25CNL   | 2-283                  |

| EP1810LC-35    | 2-65                 | TIBPAL20R8-5C      | TIBPAL20R8-7M 2-201    |

| EP1810LC-45    |                      | TIBPAL20R8-7C      | TIBPAL20R8-10M 2-221   |

| TIBPAD16N8-7C  | 2-87                 | TIBPAL20R8-10C     | TIBPAL20R8-12M 2-239   |

| TIBPAD18N8-6C  | 2-95                 | TIBPAL20R8-15C     | TIBPAL20R8-20M 2-257   |

| TIBPAL16L8-5C  | TIBPAL16L8-7M 2-103  |                    | 2-271                  |

| TIBPAL16L8-7C  | TIBPAL16L8-10M 2-123 |                    | 2-283                  |

| TIBPAL16L8-10C | TIBPAL16L8-12M 2-141 |                    | 2-283                  |

| TIBPAL16L8-12C | TIBPAL16L8-15M 2-159 |                    | 2-295                  |

| TIBPAL16L8-15C | TIBPAL16L8-20M 2-173 | TIBPAL22V10-15BC   | TIBPAL22V10-20BM 2-307 |

| TIBPAL16L8-25C | TIBPAL16L8-30M 2-187 | TIBPAL22V10AC      | TIBPAL22V10AM 2-295    |

| TIBPAL16R4-5C  | TIBPAL16R4-7M 2-103  | TIBPAL22VP10-20C   | TIBPAL22VP10-25M 2-307 |

| TIBPAL16R4-7C  | TIBPAL16R4-10M 2-123 |                    | 2-333                  |

| TIBPAL16R4-10C | TIBPAL16R4-12M 2-141 | TIBPSG507C         | TIBPSG507M 2-347       |

| TIBPAL16R4-12C | TIBPAL16R4-15M 2-159 | TIB82S105BC        | TIB82S105BM 2-363      |

| TIBPAL16R4-15C | TIBPAL16R4-20M 2-173 | TIB82S167BC        | TIB82S167BM 2-375      |

| TIBPAL16R4-25C | TIBPAL16R4-30M 2-187 |                    | 2-387                  |

| TIBPAL16R6-5C  | TIBPAL16R6-7M 2-103  | TICPAL16R4-55C     |                        |

| TIBPAL16R6-7C  | TIBPAL16R6-10M 2-123 |                    |                        |

| TIBPAL16R6-10C | TIBPAL16R6-12M 2-141 |                    | 2-387                  |

| TIBPAL16R6-12C | TIBPAL16R6-15M 2-159 |                    |                        |

| TIBPAL16R6-15C | TIBPAL16R6-20M 2-173 | TIEPAL10H16ET6C    |                        |

| TIBPAL16R6-25C | TIBPAL16R6-30M 2-187 | TEPAL10H16P8-3C    | 2-423                  |

|                |                      |                    |                        |

|                  | Page  |

|------------------|-------|

| TIEPAL10H16P8-6C | 2-429 |

| TIEPAL10H16TE6C  | 2-435 |

| TIEPAL10016ET6C  | 2-441 |

| TIEPAL10016P8-3C |       |

| TIEPAL10016TE6C  | 2-453 |

#### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### PART 1 — GENERAL CONCEPTS AND CLASSIFICATIONS OF CIRCUIT COMPLEXITY

#### Chip-Enable Input

A control input that when active permits operation of the integrated circuit for input, internal transfer, manipulation, refreshing, and/or output of data and when inactive causes the integrated circuit to be in reduced-power standby mode.

NOTE: See "chip-select input."

#### Chip-Select Input

A gating input that when inactive prevents input or output of data to or from an integrated circuit. NOTE: See "chip-select input."

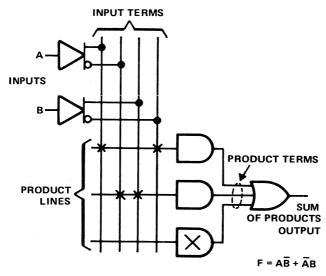

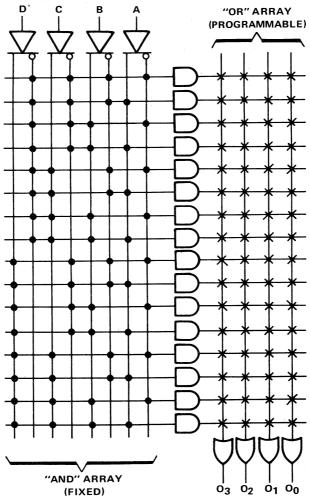

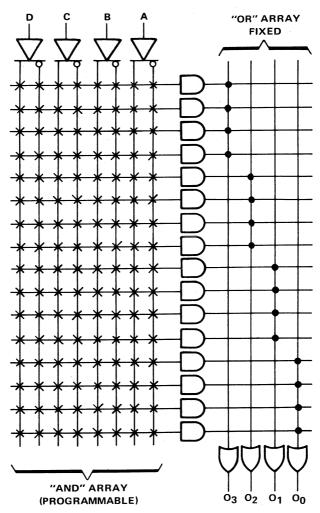

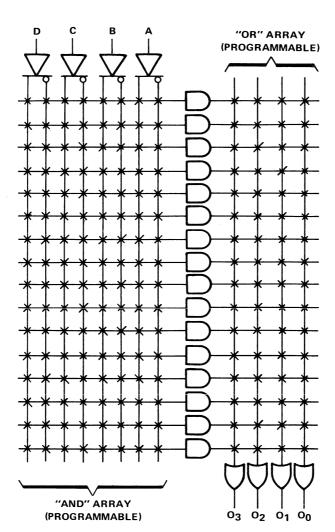

#### Field-Programmable Logic Array (FPLA)

A user-programmable integrated circuit whose basic logic structure consists of a programmable AND array and whose outputs feed a programmable OR array.

#### **Gate Equivalent Circuit**

A basic unit-of-measure of relative digital-circuit complexity. The number of gate equivalent circuits is that number of individual logic gates that would have to be interconnected to perform the same function.

#### Large-Scale Integration (LSI)

A concept whereby a complete major subsystem or system function is fabricated as a single microcircuit. In this context, a major sybsystem or system, whether digital or linear, is considered to be one that contains 100 or more equivalent gates or circuitry of similar complexity.

#### Medium-Scale Integration (MSI)

A concept whereby a complete subsystem or system function is fabricated as a single microcircuit. The subsystem or system is smaller than for LSI, but whether digital or linear, is considered to be one that contains 12 or more equivalent gates or circuitry of similar complexity.

#### **Memory Cell**

The smallest subdivision of a memory into which a unit of data has been or can be entered, in which it is or can be stored, and from which it can be retrieved.

#### **Memory Integrated Circuit**

An integrated circuit consisting of memory cells and usually including associated circuits such as those for address selection, amplifiers, etc.

#### **Output-Enable Input**

A gating input that when active permits the integrated circuit to output data and when inactive causes the integrated circuit output(s) to be at a high impedance (off).

#### **Output-Enable Input**

A gating input that when active permits the integrated circuit to output data and when inactive causes the integrated circuit output(s) to be at a high impedance (off).

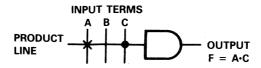

#### Programmable Array Logic (PAL®)

A user-programmable integrated circuit which utilizes proven fuse link technology to implement logic functions. Implements sum of products logic by using a programmable AND array whose outputs feed a fixed OR array.

#### Read/Write Memory

A memory in which each cell may be selected by applying appropriate electronic input signals and the stored data may be either (a) sensed at appropriate output terminals, or (b) changed in response to other similar electronic input signals.

#### Small-Scale Integration (SSI)

Integrated circuits of less complexity than medium-scale integration (MSI)

#### Typical (TYP)

A calculated value representative of the specified parameter at nominal operating conditions (V<sub>CC</sub> = 5 V,  $T_A = 25$  °C), based on the measured value of devices processed, to emulate the process distribution.

#### Very-Large-Scale Integration (VLSI)

A concept whereby a complete system function is fabricated as a single microcircuit. In this context, a system, whether digital or linear, is considered to be one that contains 3000 or more gates or circuitry of similar complexity.

PAL is a registered trademark of Monolithic Memories Inc.

## PART 2 -- OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)

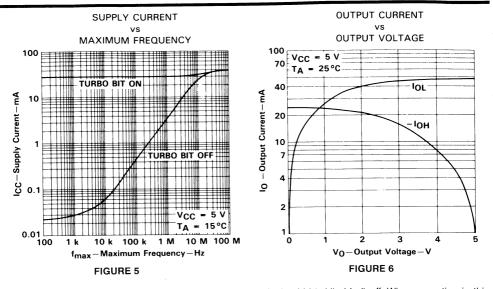

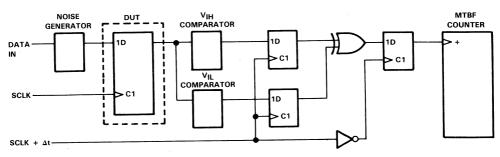

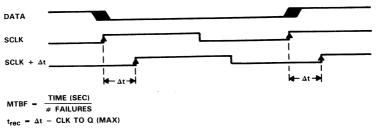

#### fmax Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

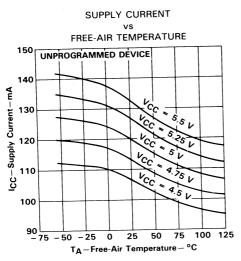

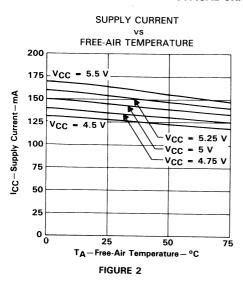

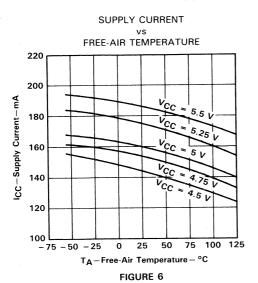

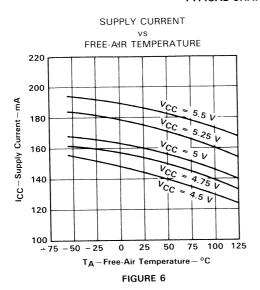

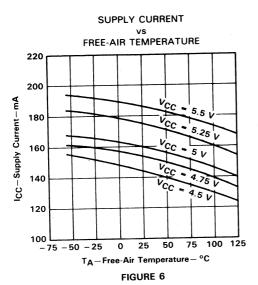

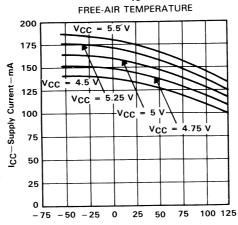

#### ICC Supply current

The current into\* the VCC supply terminal of an integrated circuit.

### ICCH Supply current, outputs high

The current into\* the VCC supply terminal of an integrated circuit when all (or a specified number) of the outputs are at the high level.

#### ICCL Supply current, outputs low

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit when all (or a specified number) of the outputs are at the low level.

#### I<sub>I</sub>H High-level input current

The current into\* an input when a high-level voltage is applied to that input.

#### IIL Low-level input current

The current into\* an input when a low-level voltage is applied to that input.

#### IOH High-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a high level at the output.

#### IOL Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output.

#### IOS (IO) Short-circuit output current

The current into\* an output when that output is short-circuited to ground (or other specified potential) with input conditions applied to establish the output logic level farthest from ground potential (or other specified potential).

# IOZH Off-state (high-impedance-state) output current (of a three-state output) with high-level voltage

The current flowing into \* an output having three-state capability with input conditions established that, according to the production specification, will establish the high-impedance state at the output and with a high-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a low level if it were enabled.

# IOZL Off-state (high-impedance-state) output current (of a three-state output) with low-level voltage applied

The current flowing into\* an output having three-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output and with a low-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a high level if it were enabled.

<sup>\*</sup>Current out of a terminal is given as a negative value.

VIH

# 1

#### High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### VIK Input clamp voltage

An input voltage in a region of relatively low differential resistance that serves to limit the input voltage swing.

#### VIL Low-level input voltage

An input voltage level within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### VOH High-level output voltage

The voltage at an output terminal with input conditions applied that, according to the product specification, will establish a high level at the output.

#### VOL Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to the product specification, will establish a low level at the output.

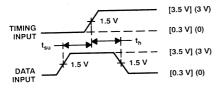

#### ta Access time

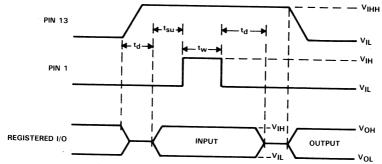

The time interval between the application of a specific input pulse and the availability of valid signals at an output.

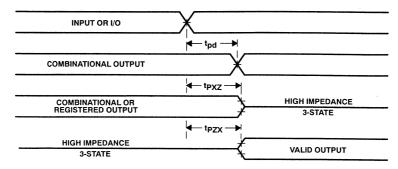

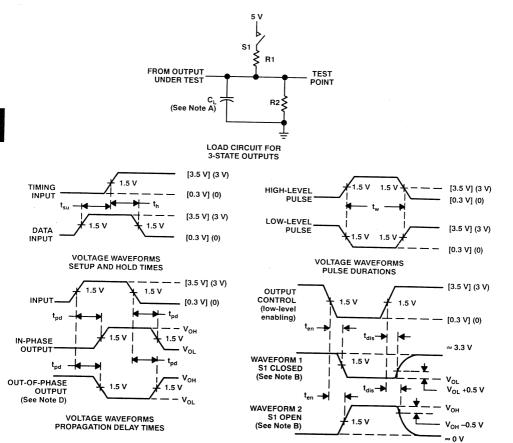

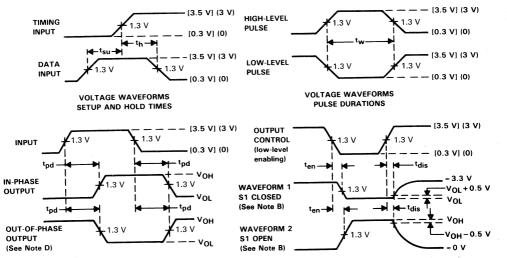

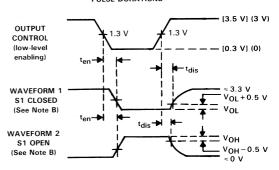

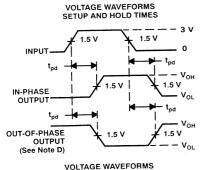

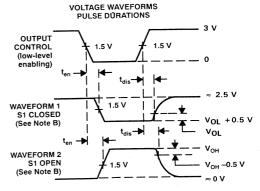

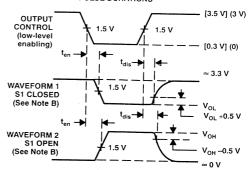

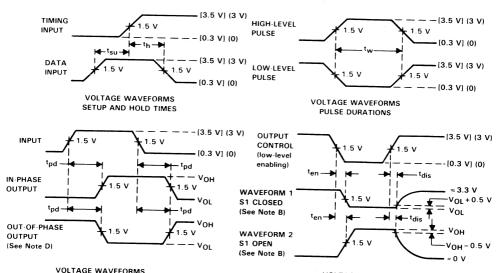

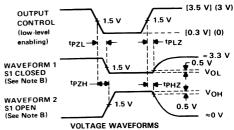

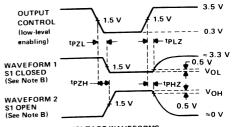

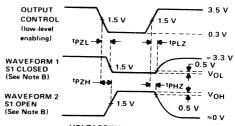

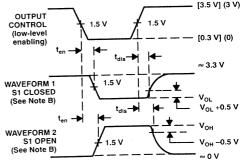

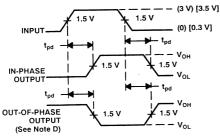

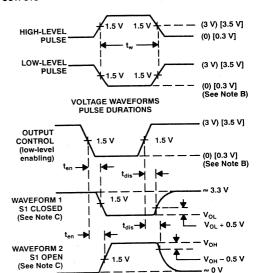

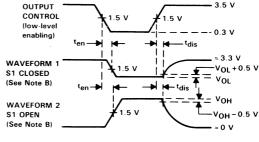

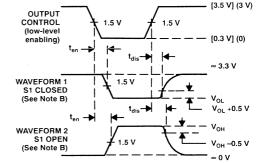

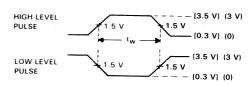

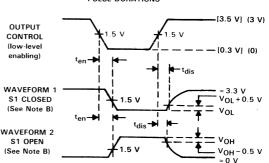

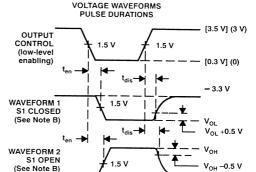

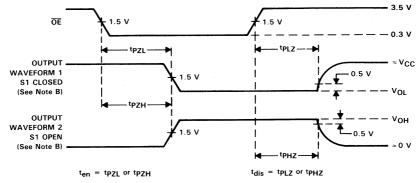

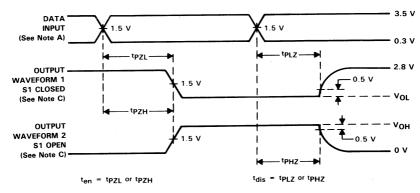

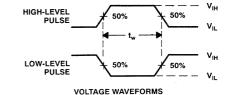

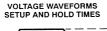

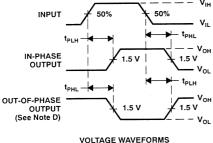

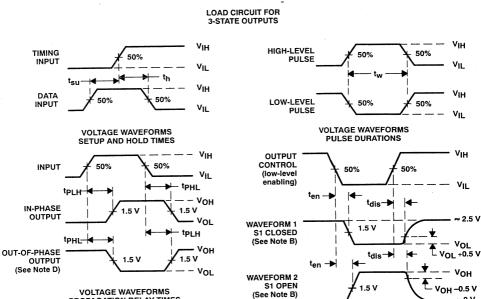

#### tdis Disable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from either of the defined active levels (high or low) to a high-impedance (off) state. ( $t_{dis} = t_{PHZ}$  or  $t_{PHZ}$ ).

#### ten Enable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from a high-impedance (off) state to either of the defined active levels (high or low). ( $t_{en} = t_{PZH}$  or  $t_{PZL}$ ).

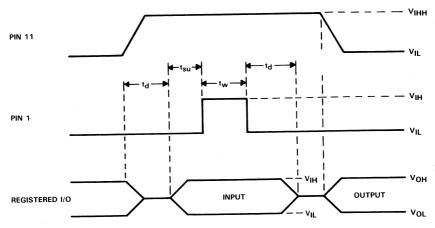

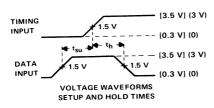

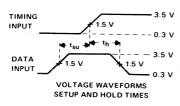

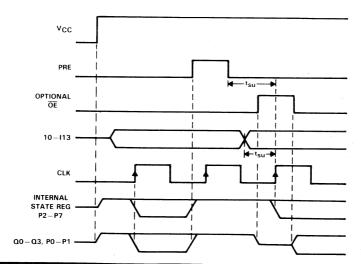

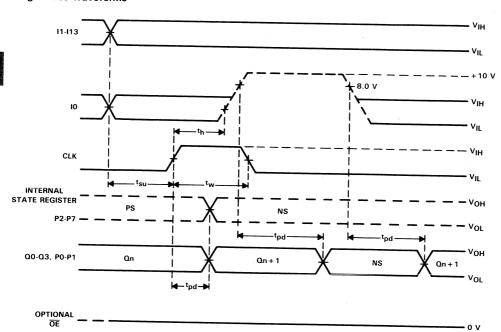

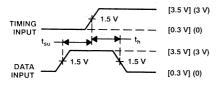

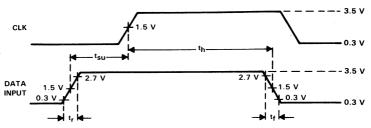

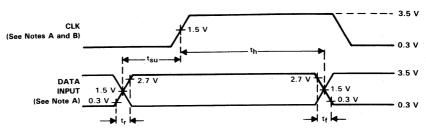

#### th Hold time

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

NOTES: 1 . The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

2. The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is guaranteed.

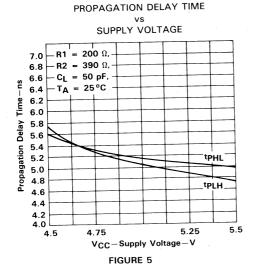

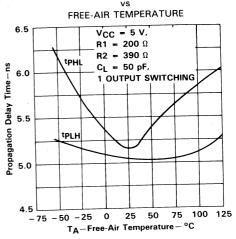

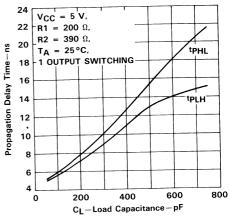

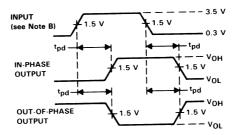

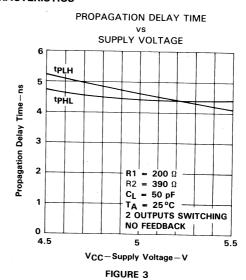

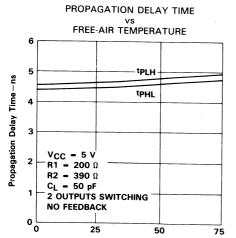

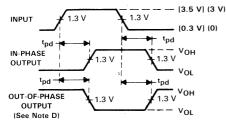

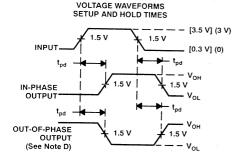

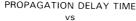

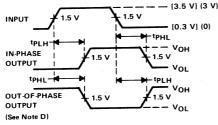

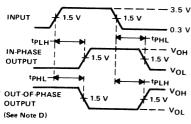

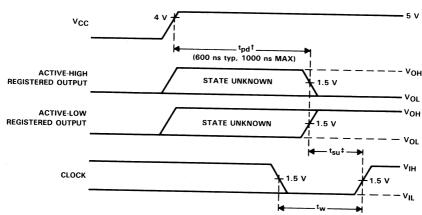

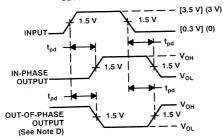

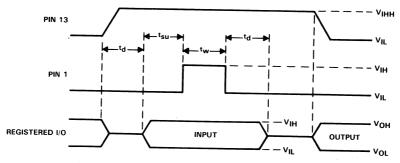

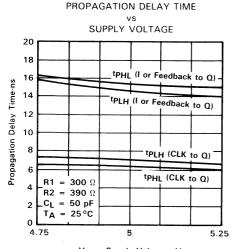

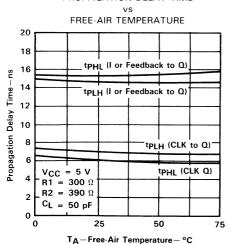

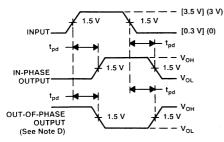

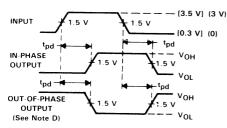

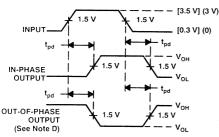

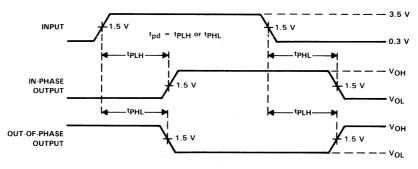

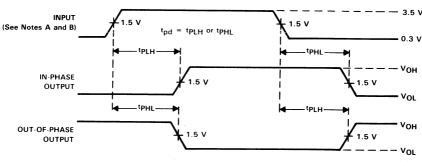

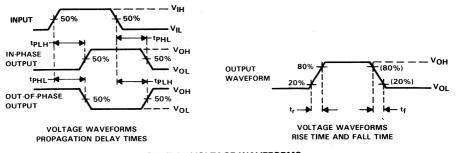

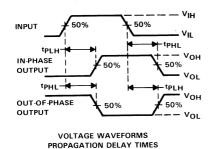

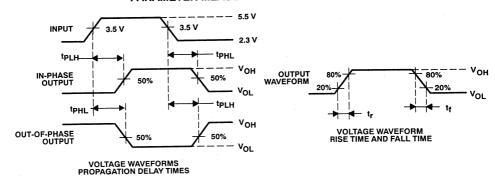

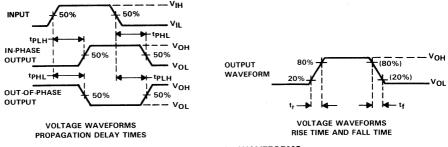

#### tpd Propagation delay time

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level. ( $t_{pd} = t_{PHL}$  or  $t_{PLH}$ ).

#### tphL Propagation delay time, high-to-low level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

#### tpHZ Disable time (of a three-state output) from high level

The time interval between the specified reference points on the input and the output voltage waveforms with the three-state output changing from the defined high level to a high-impedance (off) state.

#### tPLH Propagation delay time, low-to-high-level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

#### tpLZ Disable time (of a three-state output) from low level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from the defined low level to a high-impedance (off) state.

#### tpzH Enable time (of a three-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined high level.

#### tpzL Enable time (of a three-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined low level.

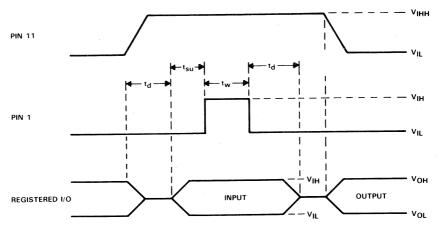

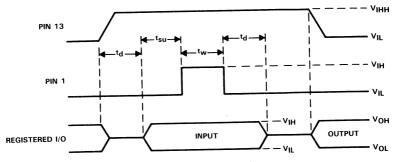

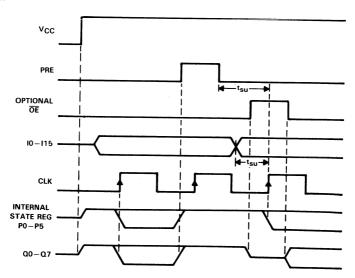

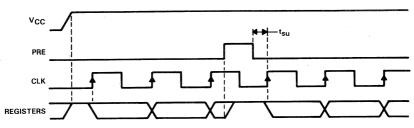

#### t<sub>SU</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

- NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- 2. The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

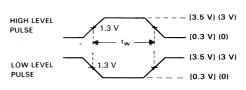

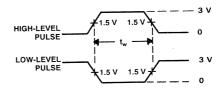

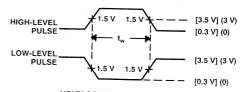

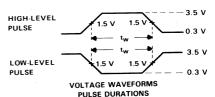

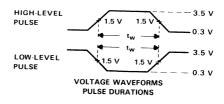

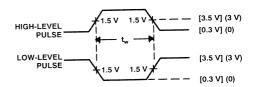

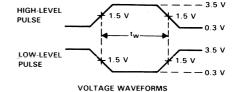

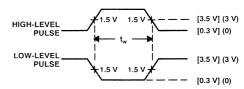

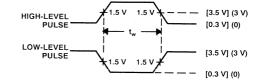

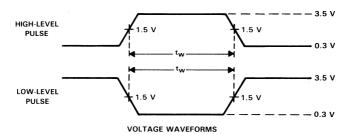

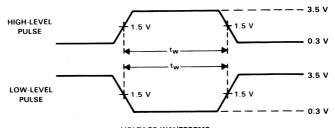

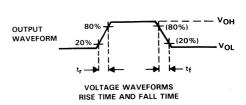

#### tw Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

The following symbols are used in function tables on TI data sheets.

H = high level (steady state)

L = low level (steady state)

↑ = transition from low to high level

↓ = transition from high to low level

→ = value/level or resulting value/level is routed to indicated destination

= value/level is reentered

X = irrelevant (any input, including transitions)

Z = off (high impedance) state of a 3-state output

a ... h = the level of steady-state inputs A through H respectively

Q<sub>0</sub> = the level of Q before the indicated steady-state input conditions were established

$\overline{\mathbb{Q}}_0$  = complement of  $\mathbb{Q}_0$  or level of  $\overline{\mathbb{Q}}$  before the indicated steady-state input conditions were

established

$Q_n$  = level of Q before the most recent active transition indicated by  $\downarrow$  or  $\uparrow$

= one high-level pulse = one low-level pulse

TOGGLE = each output changes to the complement of its previous level on each transition indicated by ↓ or ↑.

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

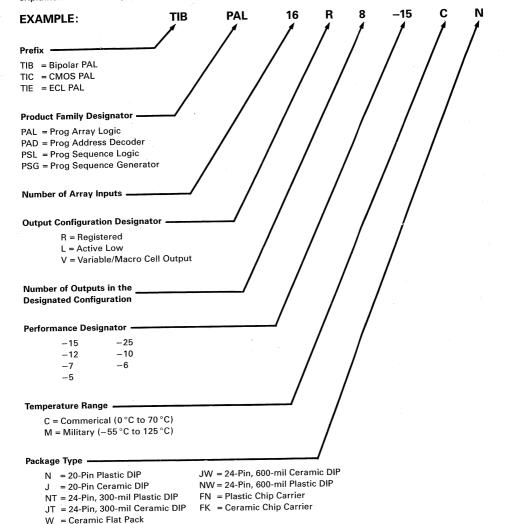

## PAL® NUMBERING SYSTEM AND ORDERING INSTRUCTIONS

Factory orders for leadership PAL® circuits described in this catalog should include a nine-part type number as explained in the example below. Exclude the prefix when ordering standard PALs.

PAL is a registered trademark of Monolithic Memories Inc.

# ADDRESSES FOR PAL® AND FPLA PROGRAMMING AND SOFTWARE MANUFACTURERS†

adams-macDonald enterprises, Inc. 800 Airport Road Monterey, CA 93940 (408) 373-3607

ADVIN SYSTEMS INC. 1050-L East Duane Ave. Sunnyvale, CA 94086 (408) 984-8600

ANVIL SOFTWARE 427-3 Amherst St. Suite 341 Nassue, NH 03063 (617) 641-3861

Bytek Corporation 508 Northwest 77th St. Boca Raton, FL 33487 (407) 994-3520

BP MICROSYSTEMS 10681 Haddington Suite # 190 Houston, TX 77043 (713) 461-9430

DATA I/0 (ABEL Design Software) 10525 Willows Road, N.E. Redmond, WA 98073-9746 (800) 247-5700

INLAB INC. (proLogic Design Software) 2150-1 West 6th Ave. Broomfield, CO 80020 (303) 460-0103 (800) 237-6759 iNt GmbH Bunsenstraße 6 8033 Martinsried West Germany (089) 857 66 67

ISDATA GmbH Haid- und Neu-Straße 7 7500 Karlsruhe 1 West Germany (07 21) 69 30 92

Kontron Messtechnik Oskar-von-Miller Straße 1 8057 Eching West Germany (08165) 77-0

LOGICAL DEVICES INC. (CUPL Design Software) 1201 N.W. 65th Place Ft. Lauderdale, FL 33309 (305) 974-0967 (800) 331-7766

MINC Incorporated (PLDesigner Software) 1575 York Road Colorado Springs, CO 80918 (719) 590-1155

Micropross Parc d'acivité des Prés 5, rue Denis Papin 59650 VILLENEUVE D'ASCQ; FRANCE (20) 47.90.40 SMS Microcomputer System Im Morgental 13 8994 Hergatz-Schwarzenberg West Germany (07522) 5018

STAG Electronic Designs Stag House Tewin Court Hertfordshire AL7 1AU United Kingdom (0707) 332148

STAG MICRO SYSTEMS 1600 Wyatt Drive Santa Clara, CA 95054 (800) 227-8836

System-General Corp. 3 Fl., No. 6, Lane 4, Tun Hwa N. Rd. P.O. Box: 53-591 Taipei, Taiwan, R.O.C. 886-2-9173005 886-2-9111283 FAX

System-General America 510 South Paric Victoria Malpitas, CA 93035 (408) 263-6667 (408) 262-9220 FAX

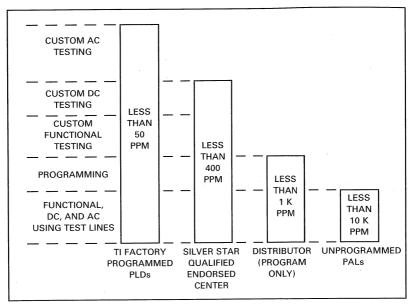

Texas Instruments does not endorse or warrant the suppliers referenced. Presently, Texas Instruments has certified DATA I/O, Sunrise, Structured Design and Digital Media. Other programmers are now in the certification process. For a current list of certified programmers, please contact your local TI sales representative.

Design and programming assistance is offered by Texas Instruments Design and Service Centers. The centers are equipped with the latest in software and hardware tools for design, debugging, prototyping, and production on a local basis. Supported by a professional engineering staff, the centers provide complete code development, device programming, symbolization, functional and DC parametric testing (Additional information is listed under chapter 3 – Test Considerations for PLDs).

#### Silver Star TI-Qualited Programming Centers

#### **Denmark**

Peter Petersen & Co A/S

Tindbjergvej 18 DK-8600 Silkeborg Tel.: 456836211

#### **Finland**

**ITT Multipomponent**

Tyopajakatu 5 PL 107 SF 00501 Helsinki Tel: 358 0 739 100

Yleislektroniikka OY

Luomannotko 6 P. O. Box 73 SF 02201 ESPOO 358 0 452 1255

#### France

**CK Electronique**

Zone D'activite de champ-fleuri Boulevard pre Pommier 38300 Bourgoin-Jallieu

Tel.: 74439471 Fax.: 74286911

#### Germany

**Electronic 2000**

Vertriebs AG Stahlgruberring 12 8000 München 82

Tel.: 089/42001-0

#### Elkose GmbH

Bahnhofstraße 44 7141 Möglingen Tel.: 07141/487-0

Enatechnik

Alfred Neye Enatechnik GmbH Schillerstraße 14 2085 Quickborn b. Hamburg Tel.: Sa.-Nr. 04106/612-0

#### iNt GmbH

Bunsenstraße 6 8033 Martinsried Tel.: (089) 857 66 67

Neumüller GmbH

Eschenstraße 2 8028 Taufkirchen/München

Tel.: 089/61208-0

Spoerle Electronic

Max-Planck-Straße 1–3 6072 Dreieich 1 Tel.: 0 61 03/3 04-0

#### Holland

Koningen Hartman

Elektrotechnik B.V. Energieweg 1 2627 AP Delft

Tel.: (015) 609906

#### Rood Testhouse B.V.

Brugstraat 2 P.O. Box 90 8180 AB Heerde

Tel.: (0) 5782-9200

#### Texim Electronics B.V.

Albert Cuyplaan 4 7482 Ja Haaksbergen Tel.: 31-5427-33333

#### Norway

**ETS**

Kapermoen 22 3600 Kongsberg Tel.: 03-735100

#### Jakob Hatteland Electronic A/S N-5578 Nedre Vats

Tel.: 47 3 76 51 11

#### Schweiz

**FABRIMEX AG**

Kirchenweg 5 CH-8032 Zürich Tel.: 01/2512929

#### Sweden

**AB Gosta Backstrom**

Alstromergatan 22 Box 12009 S-102 21 Stockholm

Tel.: 46-8-54 1080

#### **Endorsed Program and Test Center**

**SES Electronics GmbH**

Oettinger Straße 6 D-8860 Nördlingen Tel.: (09081) 804-0

| Data Sheets                   |    | 2 |

|-------------------------------|----|---|

|                               |    |   |

|                               |    |   |

|                               |    |   |

|                               |    |   |

|                               |    |   |

| PAL Support                   |    | 5 |

|                               |    |   |

|                               |    |   |

|                               |    |   |

|                               |    |   |

|                               |    |   |

| <b>EPLD Development Syste</b> | ms | 4 |

|                               |    |   |

|                               |    |   |

|                               |    |   |

|                               |    |   |

|                               |    |   |

| Mechanical Data               |    | L |

| [[[]]]                        |    | - |

**General Information**

# EP330 HIGH-PERFORMANCE 8-MACROCELL ERASABLE PROGRAMMABLE LOGIC DEVICE (EPLD) D3374, OCTOBER 1989

- Programmable Replacement for Conventional TTL, 74HC, and 20-Pin PAL® Family

- UV-Light-Erasable Cell Technology Provides:

- Reconfigurable Logic

- Reprogrammable Cells

- Full Factory Testing for 100%

Programming Yields

- High-Voltage EPIC™ Process Allows for Higher Performance as follows:

- User-Programmable Output Logic Macrocells Provide Flexibility in Output Types with:

- Selectable for Registered or Combinational Operation

- Output Polarity Control

- Independently User Programmable Feedback Path

- Programmable Design-Security Bit Prevents Copying of Logic Stored in Device

- Advanced Software Support Featuring Schematic Capture, Interactive Netlist, Boolean Equations, and State-Machine Design Entry

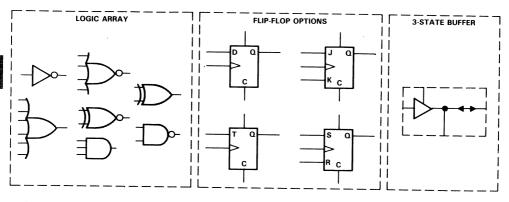

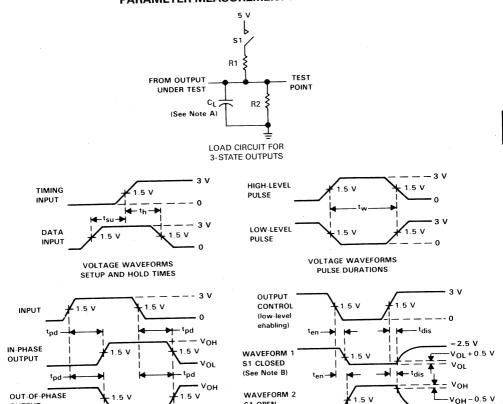

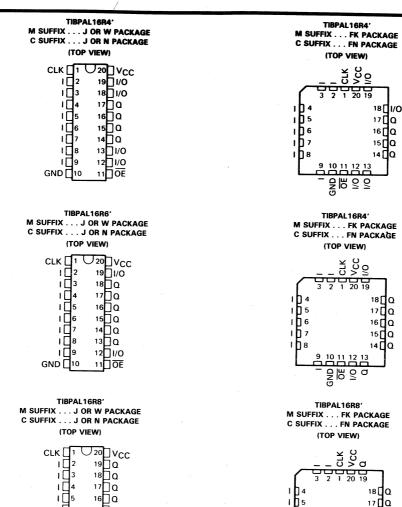

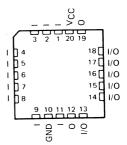

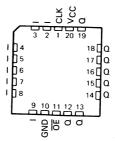

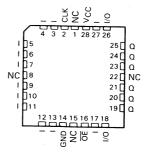

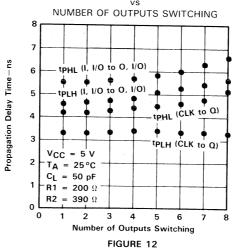

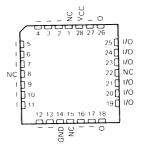

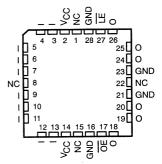

J OR N PACKAGE (TOP VIEW)

FN PACKAGE

Pin assignments in operating mode

- · Package Options Include:

- 20-pin Ceramic Dual-In-Line (J) UV-erasable

- 20-pin Plastic Dual-In-Line (N) One-Time Programmable

- 20-pin Plastic Chip Carrier (FN) One-Time Programmable

#### description

#### general

The EP330 features advanced-CMOS speed and very low power. It combines the High-Voltage Enhanced-Processed Implanted CMOS (HVEPIC\*\*) process with ultraviolet-light-erasable technology. Each output has an Output-Logic-Macrocell (OLM) configuration that allows user definition of the output type. This EPLD provides a reliable low-power substitute for numerous high-performance TTL PALs.

#### **AVAILABLE OPTIONS**

|                         |                                      | PACKAGE TYPE |                                |                                 |  |  |

|-------------------------|--------------------------------------|--------------|--------------------------------|---------------------------------|--|--|

| T <sub>A</sub><br>RANGE | SPEED CERAMIC CLASS DUAL-IN-LINE (J) |              | PLASTIC<br>DUAL-IN-LINE<br>(N) | PLASTIC<br>CHIP CARRIER<br>(FN) |  |  |

| -55°C to 125°C          | 25 ns                                | EP330-25MJB  | N/A                            | N/A                             |  |  |

| -40°C to 85°C           | 20 ns                                | EP330-20IJ   | EP330-20IN                     | EP330-20IFN                     |  |  |

| 0°C to 70°C             | 15 ns                                | EP330-15CJ   | EP330-15CN                     | EP330-15CFN                     |  |  |

EPIC is a trademark of Texas Instruments Incorporated. PAL is a registered trademark of Monolithic Memories, Inc.

#### description (continued)

The EP330 can accommodate up to 18 inputs and up to eight outputs. The 20-pin 300-mil package contains eight macrocells each using a programmable AND/fixed-OR structure. This AND-OR structure yields eight product terms for the logic function as well as an individual term for Output Enable.

The EP330 output-logic macrocell allows the user to configure output and feedback paths for combinational or registered operation either active high or active low. With a  $t_{pd}$  of 15 ns, the EP330 may be configured as a low-power substitute for popular PAL devices such as the PAL16XXB series or the PAL16XX-15 series.

The CMOS EPROM technology makes it possible for the EP330 to operate at an active power-consumption level that is less than 75% of equivalent bipolar devices without sacrificing speed performance. This technology also facilitates 100% generic testability as well as UV-light erasability. As a result, designs and design modification can be quickly effected with a given EP330 without the need for post-programming testing.

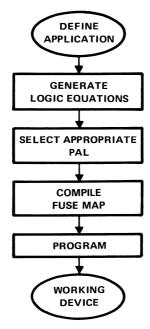

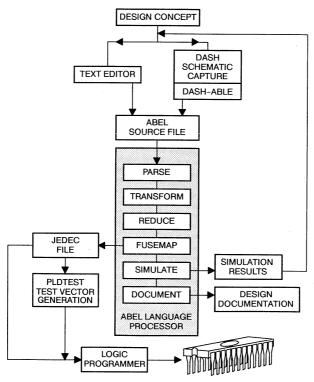

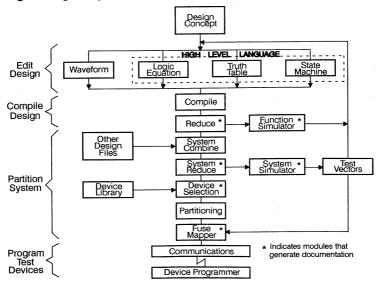

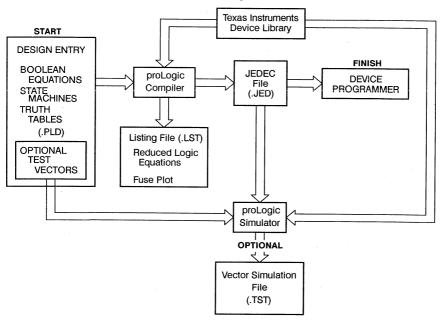

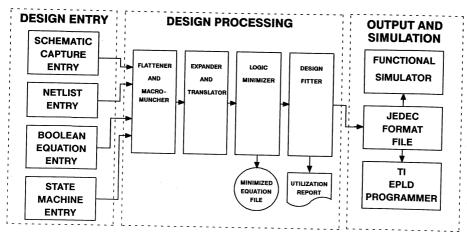

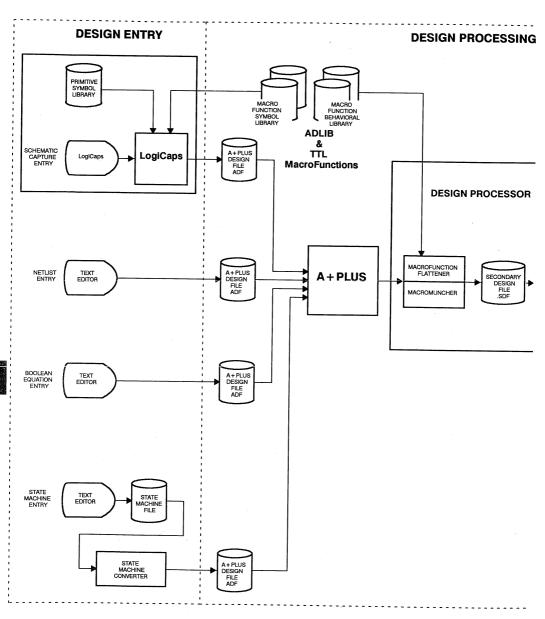

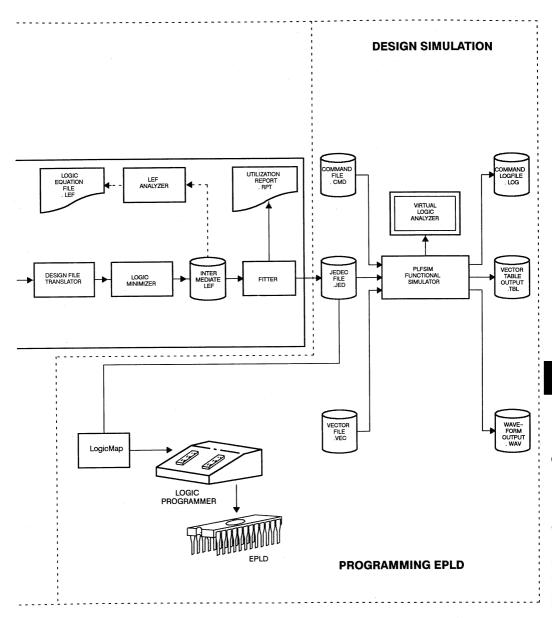

Programming the EP330 is accomplished with the use of the TI EPLD development system, which supports four different design entry methods. When the design has been entered, the A+PLUS software (which is the heart of the development system) performs automatic translation into logical equations, performs complete Boolean minimization, and fits the design directly into an EP330. The device can then be programmed to achieve customized working silicon within minutes at the designer's desk.

The EP330M is characterized for operation over the full military temperature range of  $-55^{\circ}$ C, to  $125^{\circ}$ C. The EP330I is characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C. The EP330C is characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C.

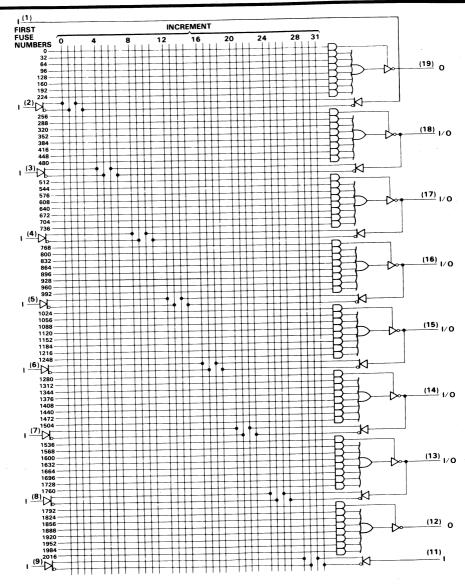

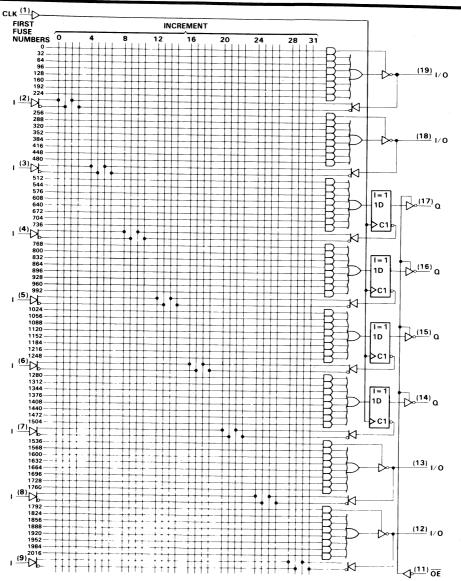

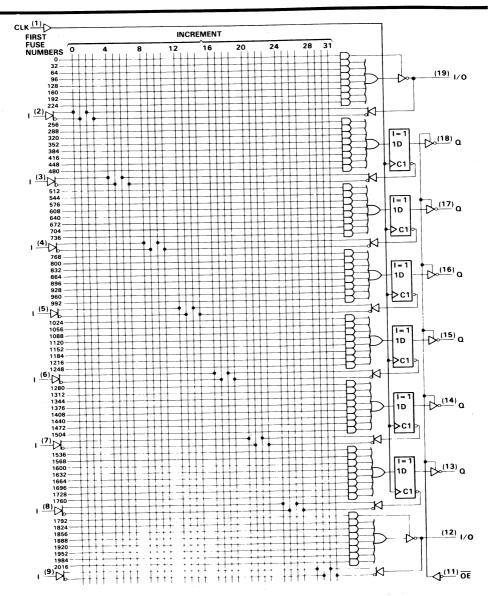

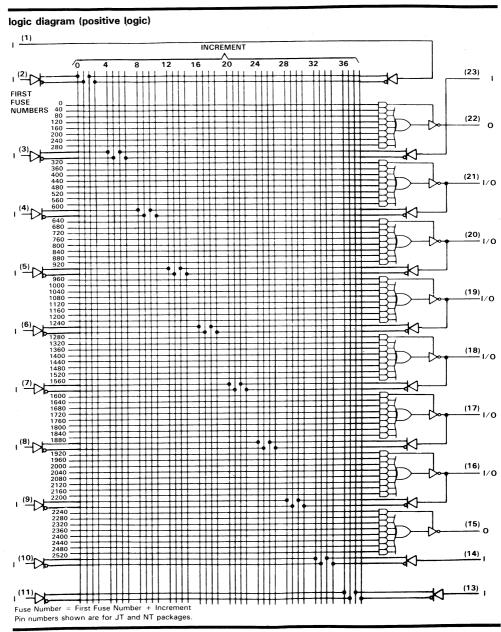

#### functional description

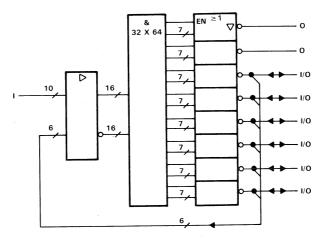

Externally, the EP330 provides ten dedicated inputs (one of which may be used as a synchronous clock input) and eight I/O pins that may be configured for input, output, or bidirectional operation.

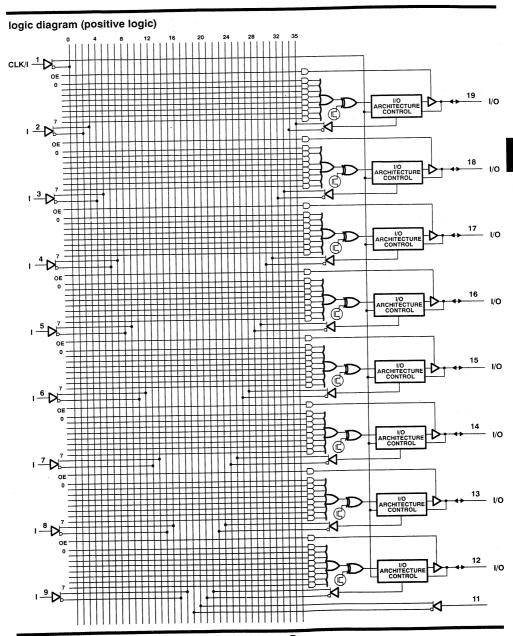

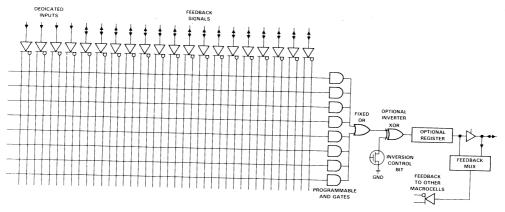

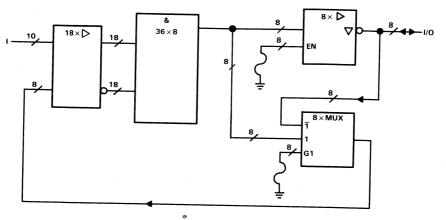

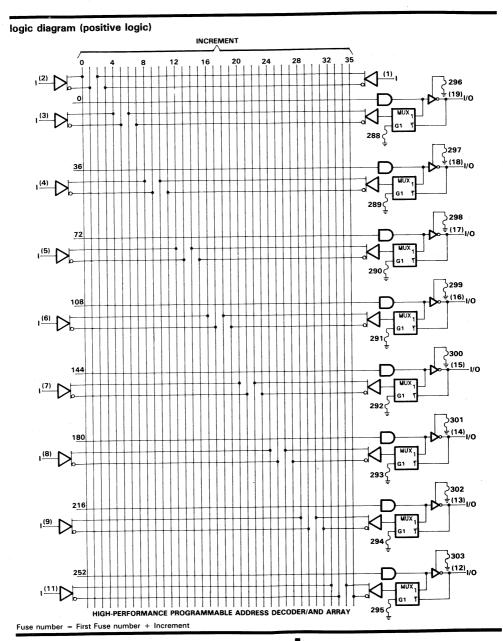

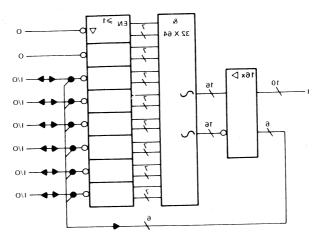

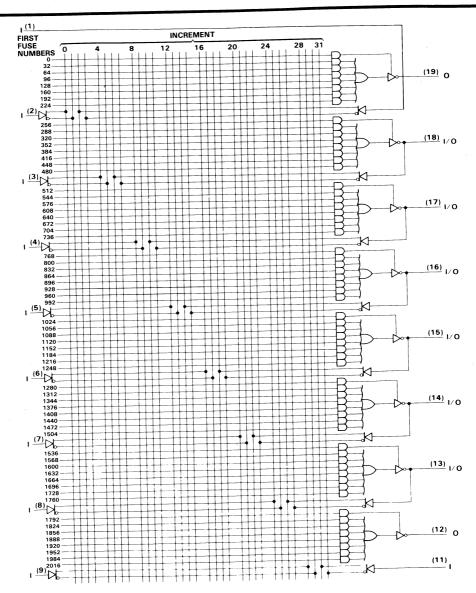

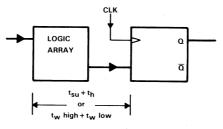

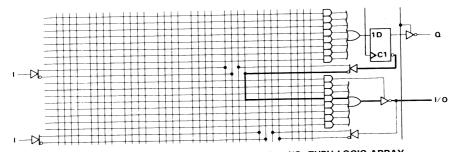

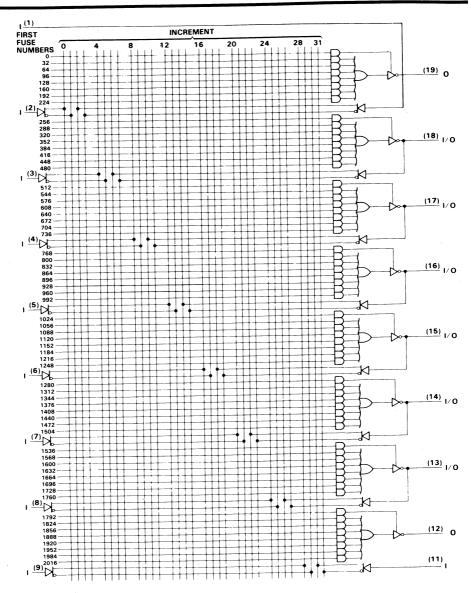

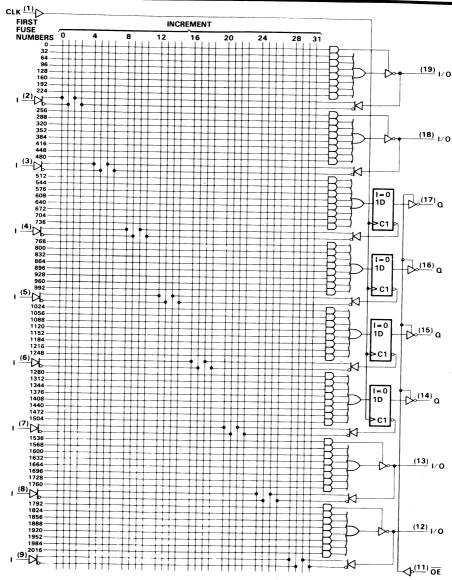

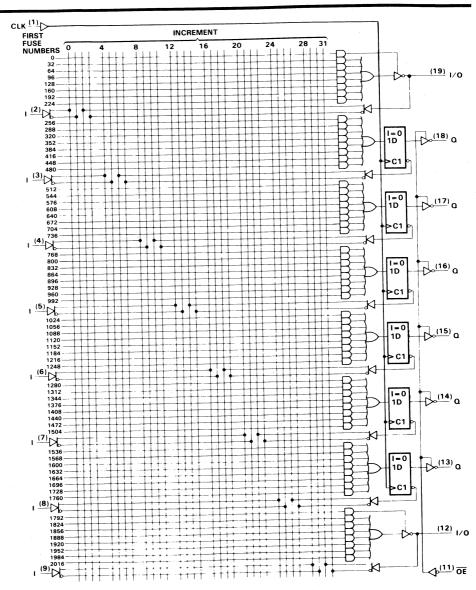

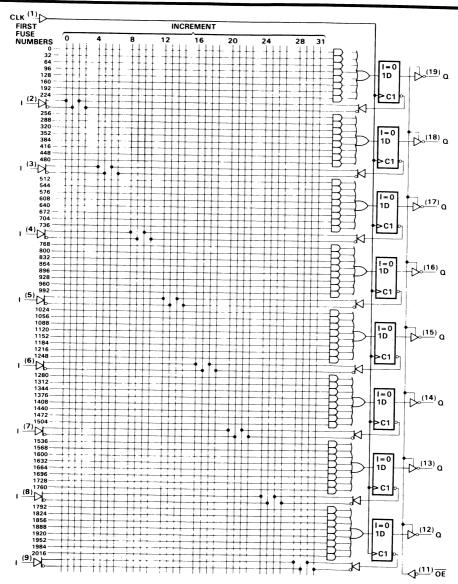

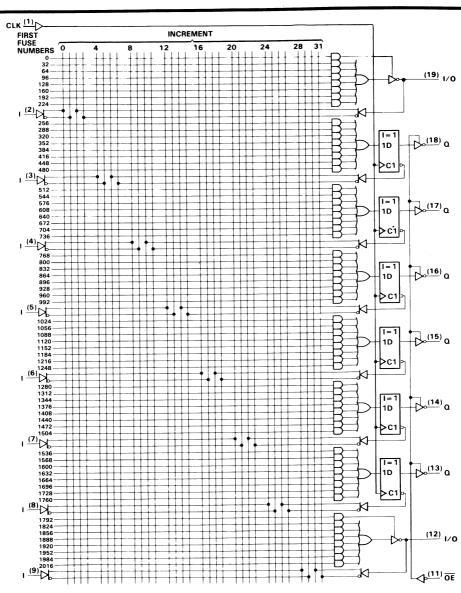

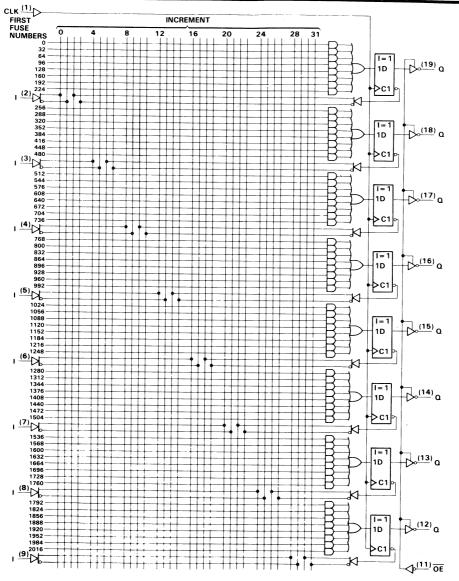

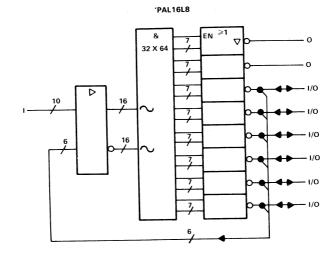

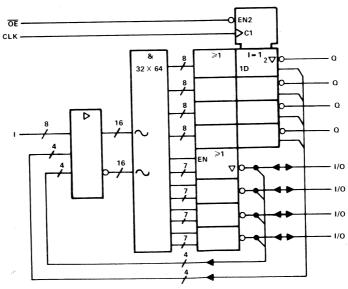

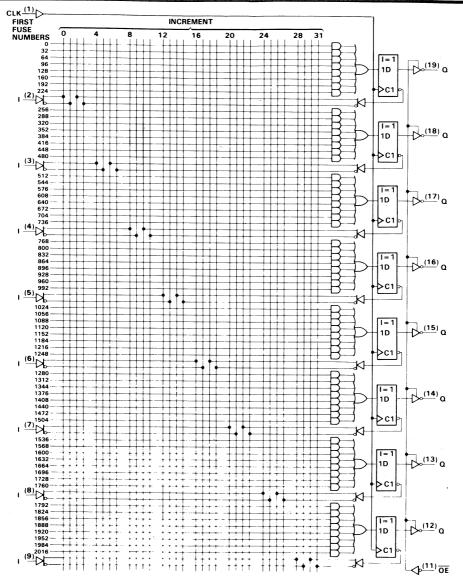

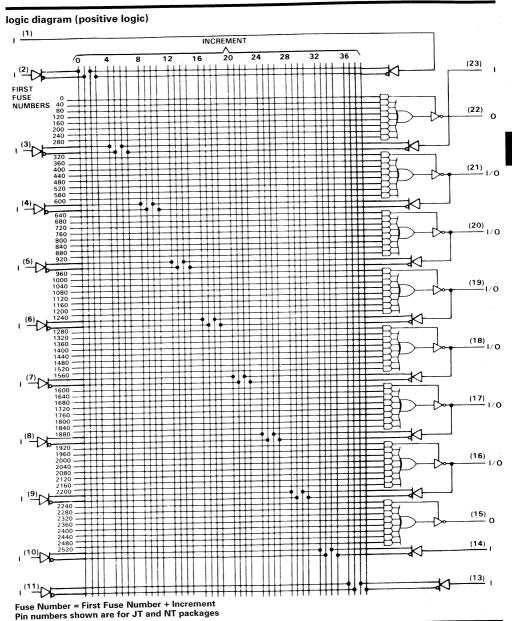

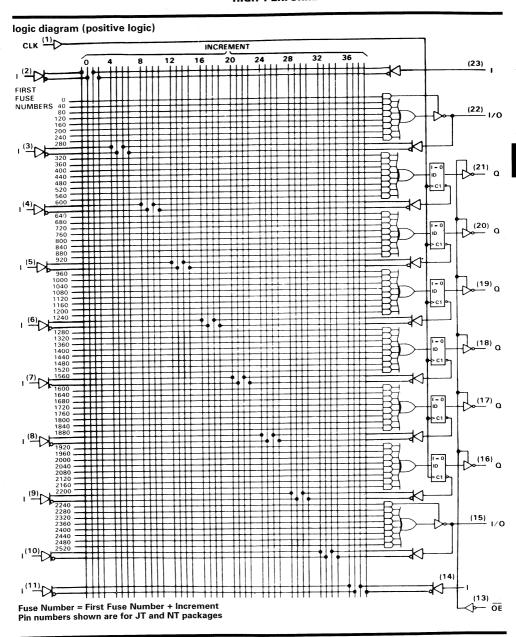

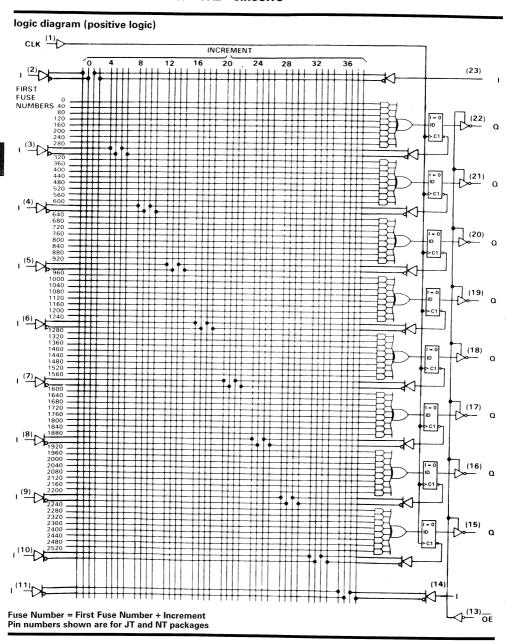

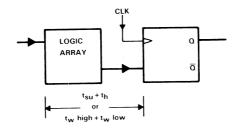

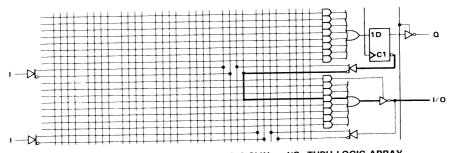

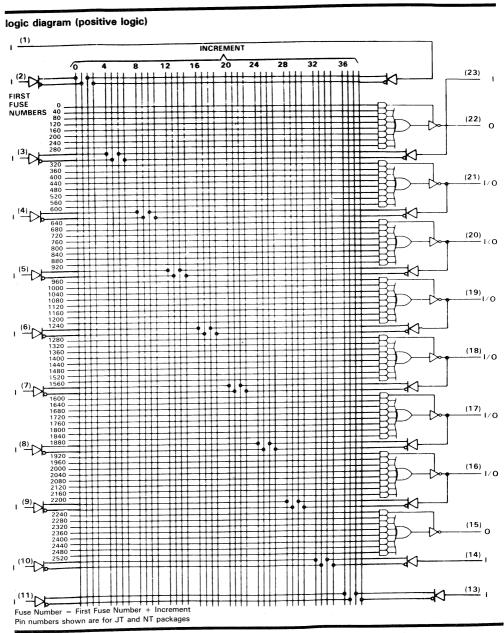

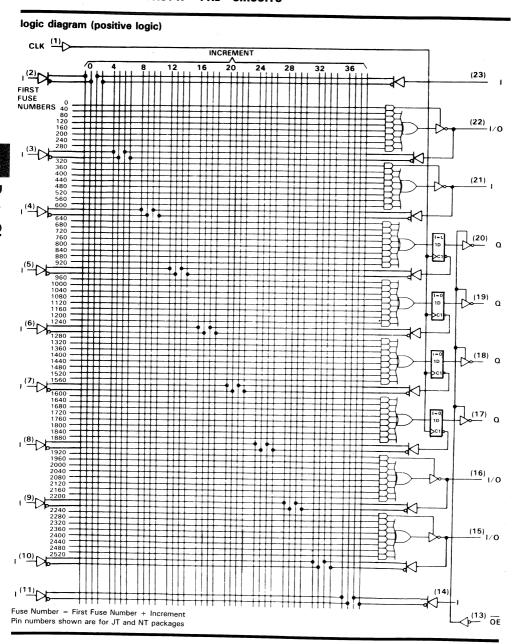

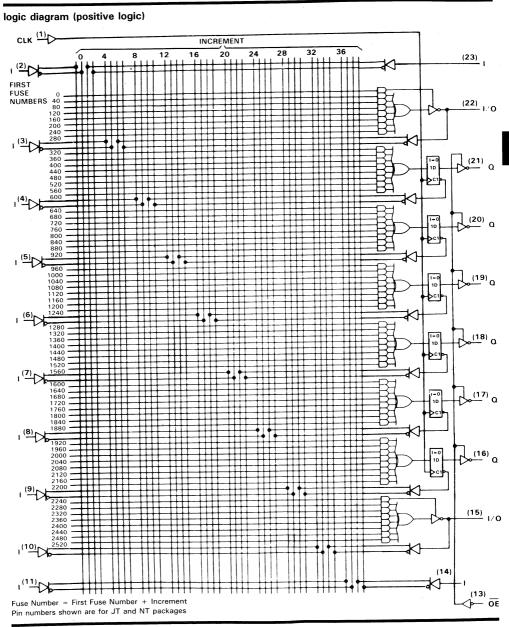

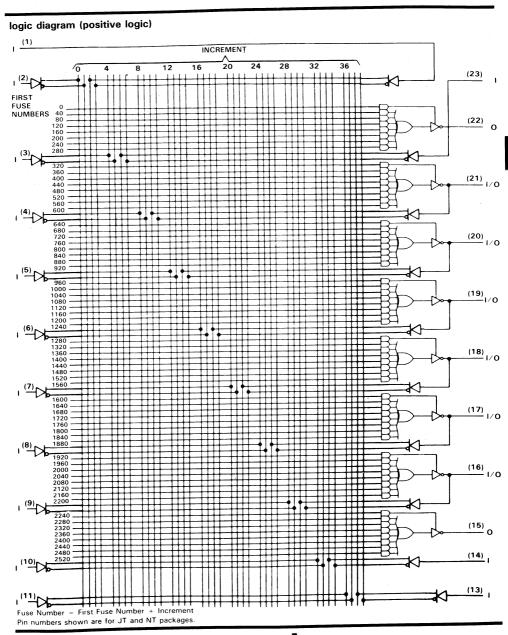

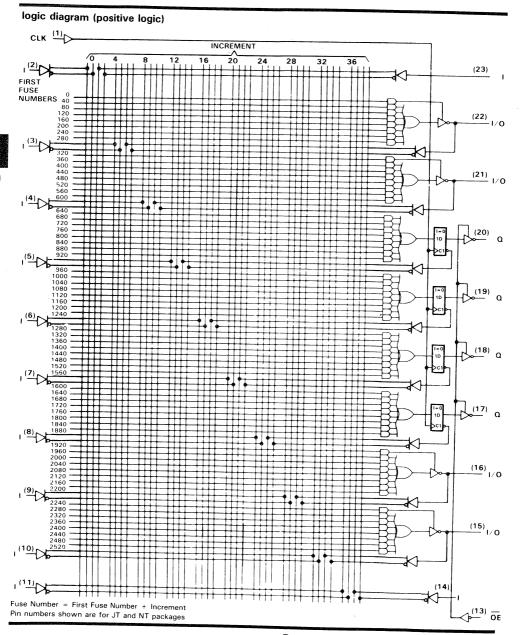

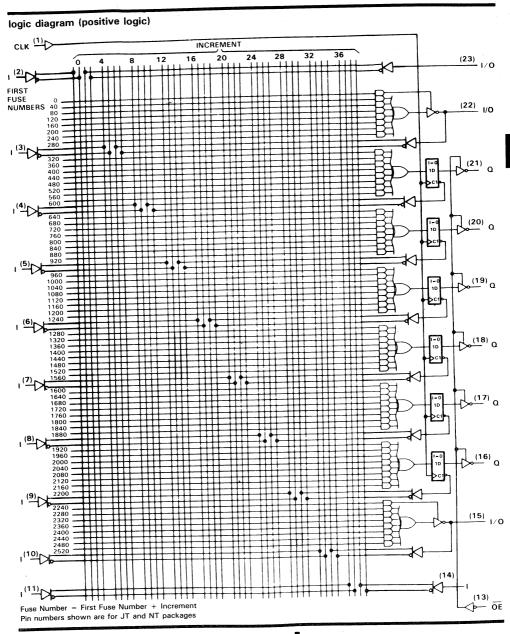

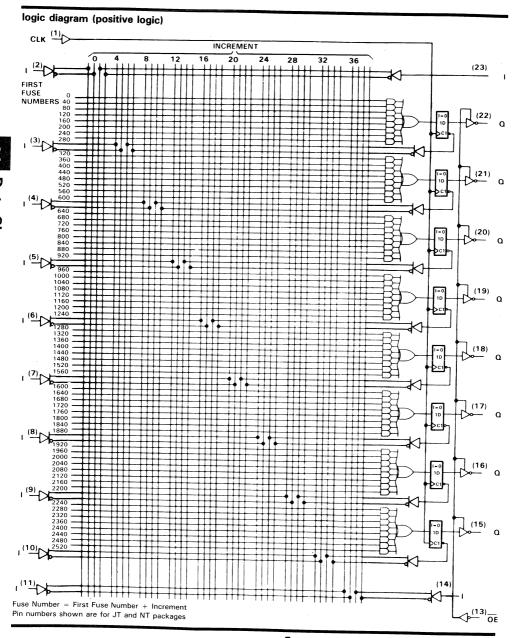

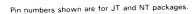

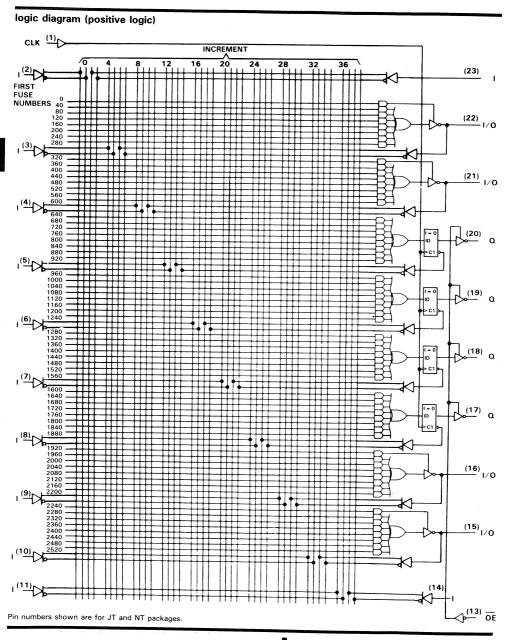

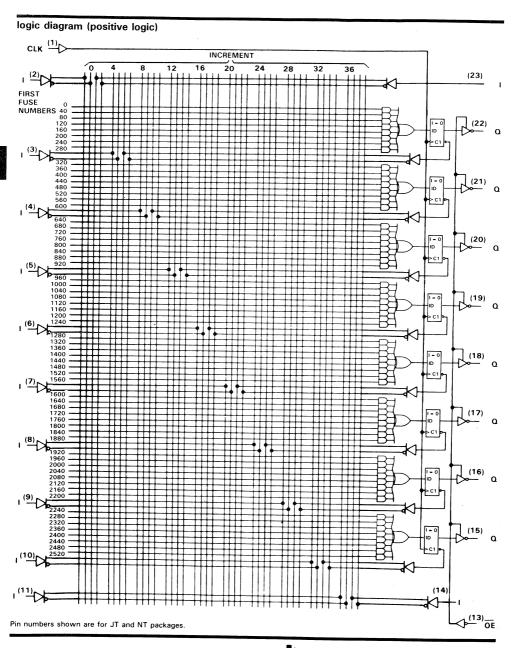

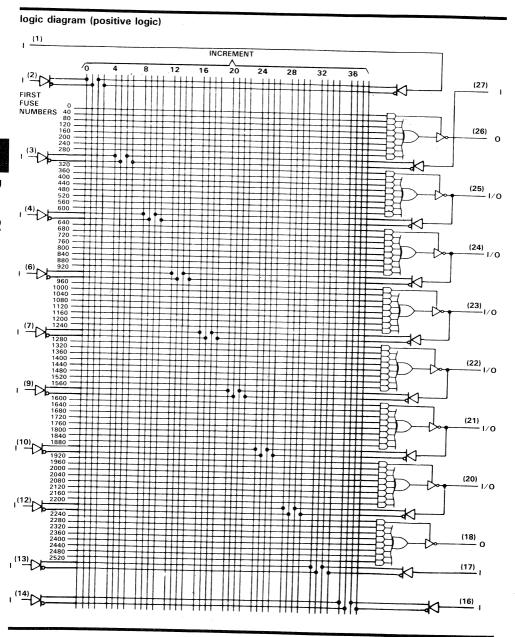

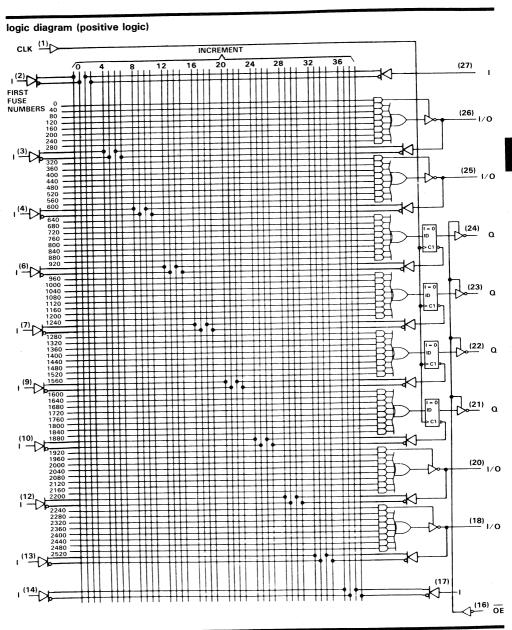

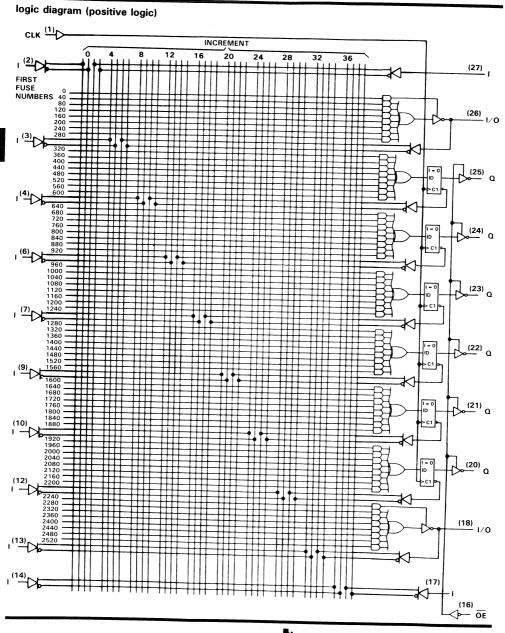

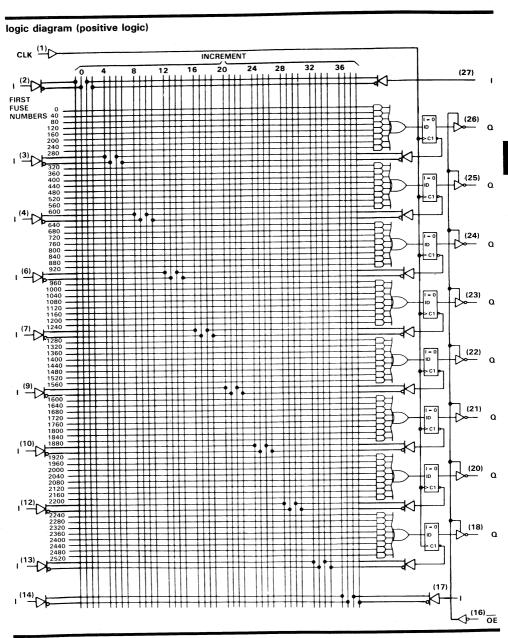

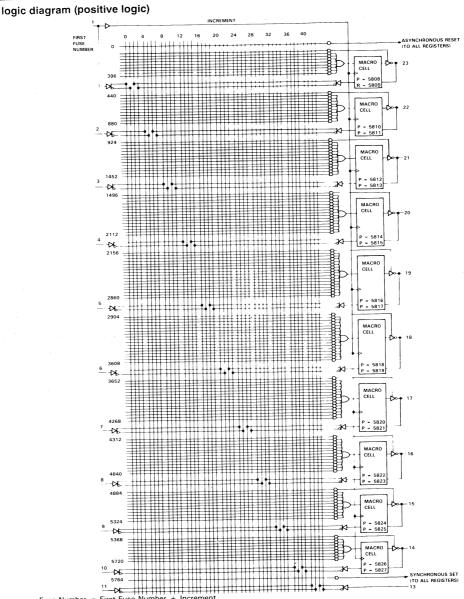

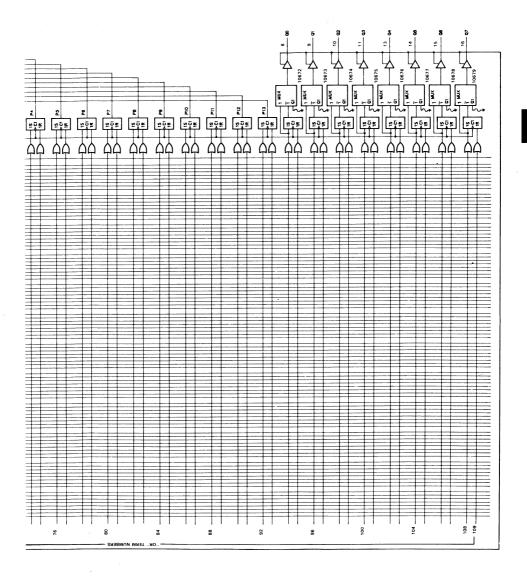

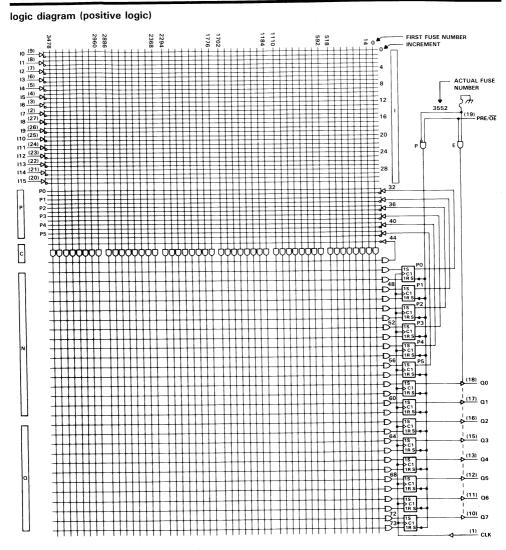

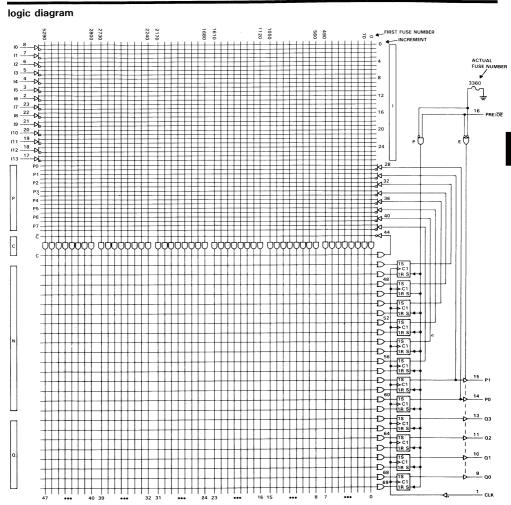

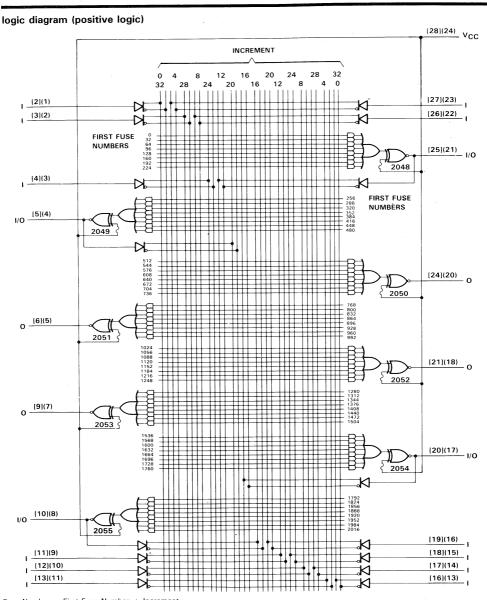

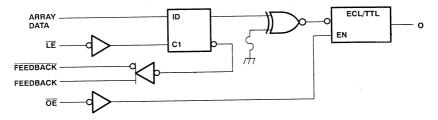

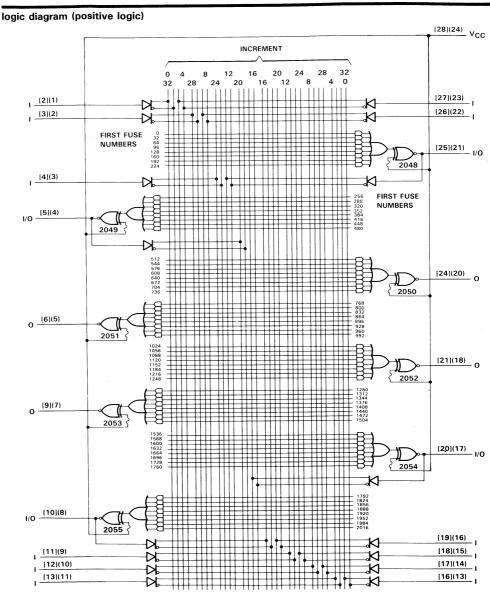

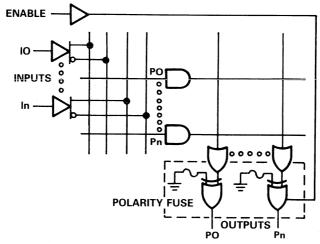

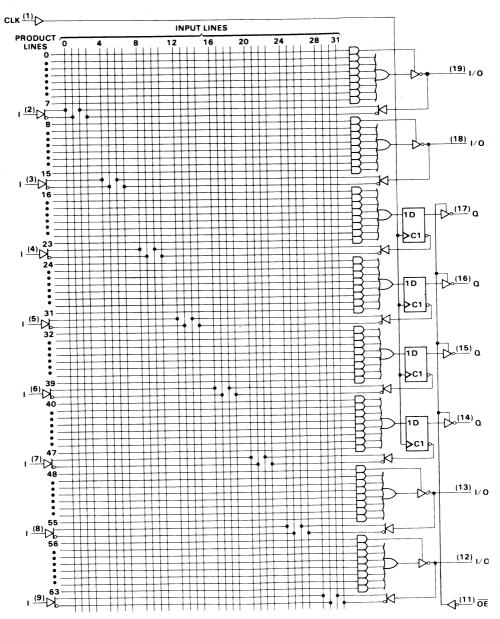

The logic diagram shows the complete EP330, while Figure 1 shows the basic EP330 macrocell. The internal architecture is organized with the familiar sum of products (AND-OR) structure. Inputs to the programmable AND array (shown running vertically in Figure 1) come from two sources: first, the true and complement of the ten dedicated input pins and second, the true and complement of the eight feedback signals, each one originating from an I/O architecture-control block. The 36-input AND array encompasses a total of 72 product terms distributed equally among the eight macrocells. Each product term (shown running horizontally in the logic diagram) represents a 36-input AND gate.

As shown in the logic diagram, the outputs of eight product terms are ORed together, then the output of the OR gate is sent as an input to an exclusive-OR gate. The purpose of this exclusive-OR gate is to allow the user to specify the polarity of the output signal by using the invert-select EPROM cell (active high if the EPROM cell is programmed and active low if it is not programmed).

The exclusive-OR output then feeds the I/O architecture control block. The control block configures the output for registered or combinational operation. In the registered configuration, the output is registered via a positive edge-triggered D-type flip-flop. In this condition, the feedback signal going to the array is also registered and comes directly from the output of the D-type flip-flop. In the combinational configuration, the output is nonregistered and the feedback signal comes directly from the I/O pin. In the erased state, the EP330 contains the same architectural characteristics as the PAL16L8.

- NOTES: A. This diagram shows one of the eight macrocells within the EP330.

- B. The double-arrow lines (\*) show I/O feedback from a macrocell.

#### FIGURE 1. LOGIC ARRAY MACROCELL

#### output-enable product term

The output enable (OE) product term determines whether an output signal is allowed to propagate to the output pin. If the output of the OE product term is low, then the output buffer becomes a high-impedance node, thus inhibiting the output signal from reaching the output pin. For combinational configurations, this OE product term can be used to allow for true bidirectional operation.

The EP330 contains eight separate OE product terms, one per I/O pin. If it is desired that all outputs be enabled or disabled simultaneously, use an identically programmed product term at each of the outputs. If different outputs are to be enabled under different conditions, different OE product terms for each specific output may be defined.

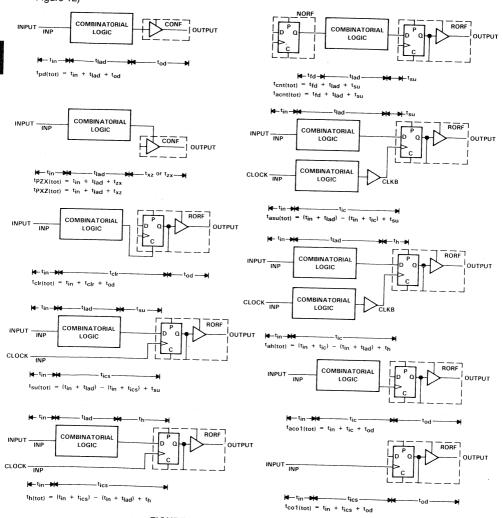

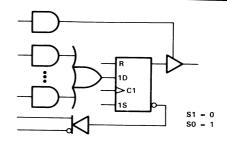

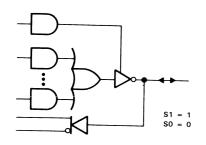

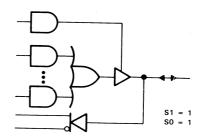

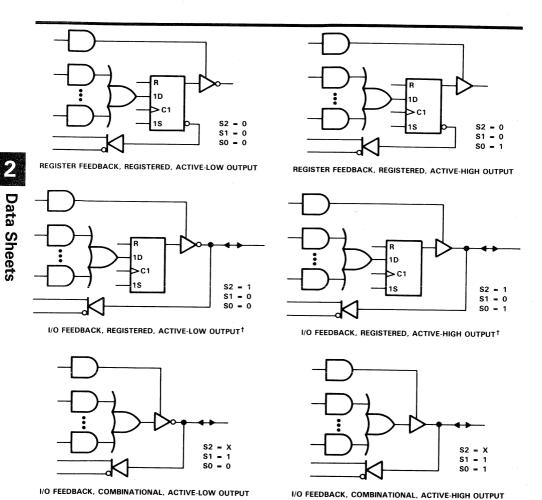

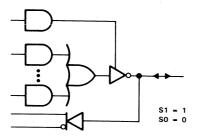

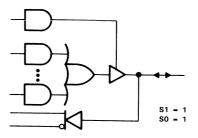

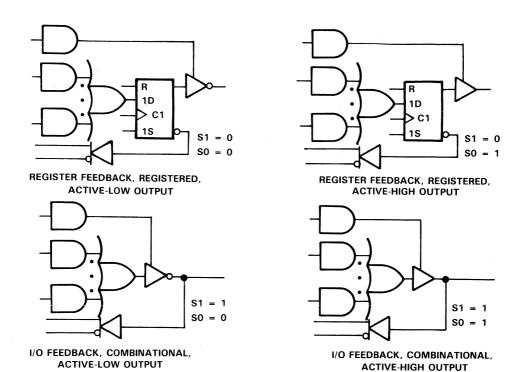

#### I/O architecture

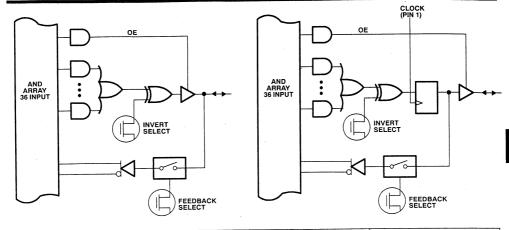

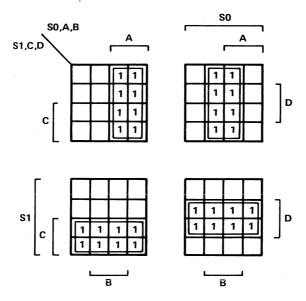

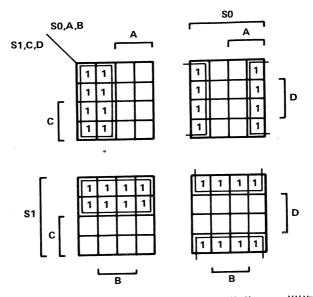

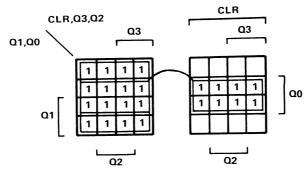

Figure 2 shows the different output configurations that can be chosen for any of the eight I/O pins on the EP330. Because of the individuality of each I/O architecture control block, both registered and combinational output can be chosen on a given EP330 device.

In the combinational configuration, either active-high or active-low output polarity can be chosen. Pin feedback or no feedback is also optional. In the registered configuration, the user has control over output polarity and may choose to use the internal feedback path or no feedback. Any I/O pin can be configured as a dedicated input by choosing no output and no feedback from the array. In the erased state, the I/O architecture is configured for a combinational active-low output with pin feedback.

| OUTPUT/POLARITY    | FEEDBACK  | OUTPUT/POLARITY | FEEDBACK         |

|--------------------|-----------|-----------------|------------------|

| Combinational/High | Pin, None | D Register/High | D Register, None |

| Combinational/Low  | Pin, None | D Register/Low  | D Register, None |

| None               | Pin       | None            | D Register       |

(a) Combinational Configuration

(b) Registered Configration

FIGURE 2. I/O CONFIGURATIONS

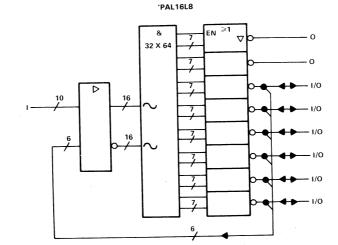

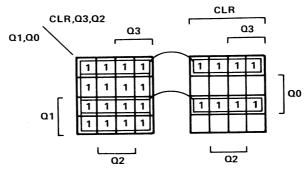

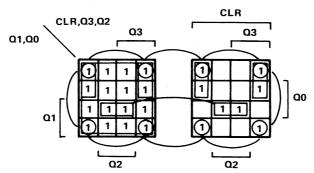

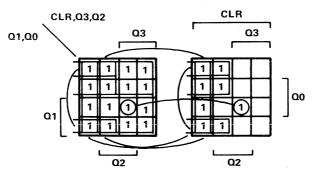

#### PAL compatibility

Figures 2(a) and 2(b) show how an EP330 can be configured as a drop-in replacement for two commonly used members of the 20-pin PAL family: the PAL16L8 and the PAL16R8. When configured in these manners, the EP330 is both a functional replacement, as well as a pin-to-pin replacement, for the PAL16L8 and PAL16R8.

Tables 1 and 2 provide additional information concerning the EP330 as a replacement for the 20-pin PAL family of devices.

- "Invert Select" EPROM cell is in the erased state providing active-low outputs.

- "Combinational Mode" is chosen providing Combinational Output with Input (Pin) Feedback (COIF).

- 8-product-term OR gate compared to 7-product-term OR gate on PAL16L8.

- Pin feedback to the array at 12 through 19 is not available in PAL16L8.

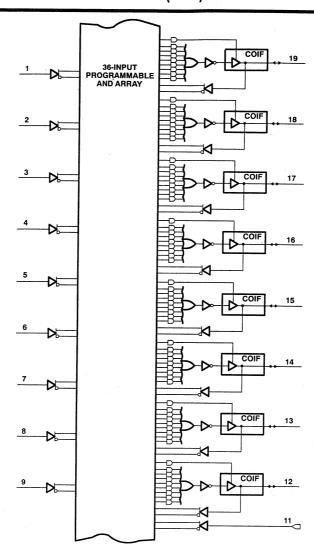

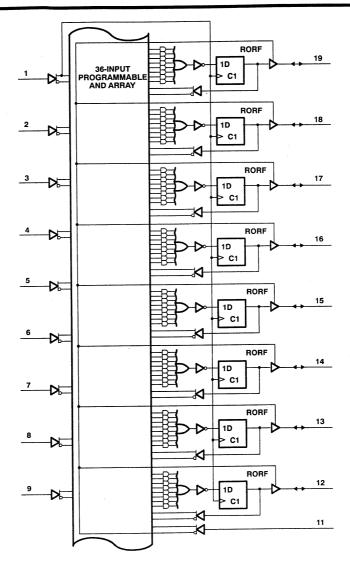

FIGURE 3. EP330 CONFIGURATION FOR REPLACING A PAL16L8

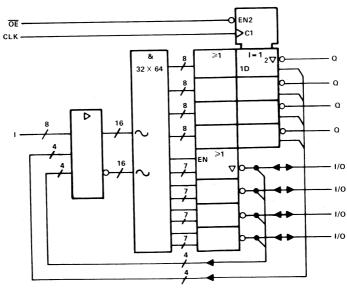

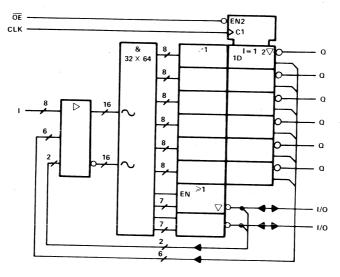

- "Invert Select" EPROM cell is in the erased state providing active-low outputs.

- "Registered Mode" is chosen providing Registered Output with Registered Feedback (RORF).

- Complement of pin 11 is used as common OE term for all eight output pins.

FIGURE 4. EP330 CONFIGURATION FOR REPLACING A PAL16R8

### TABLE 1. CONFIGURATIONS FOR 20-PIN PAL REPLACEMENT

| PAL         | EP330 EP330 |                  | I/O                | OUTPUT/                    | FEEDBAC |

|-------------|-------------|------------------|--------------------|----------------------------|---------|

| PART NUMBER | PIN NUMBER  | MACROCELL NUMBER | CONFIGURATION MODE | POLARITY                   | FEEDBAC |

| 10H8        | 12-19       | 1-8              | Combinational      | Comb/High                  | None    |

| 10L8        | 12-19       | 1-8              | Combinational      | Comb/Low                   | None    |

|             | 12          | 8                | Combinational      | None                       | Pin     |

| 12H6        | 13-18       | 2-7              | Combinational      | Comb/High                  | None    |

|             | 19          | 1                | Combinational      | None                       | Pin     |

|             | 12          | 8                | Combinational      | None                       | Pin     |

| 12L6        | 13-18       | 2-7              | Combinational      | Comb/Low                   | None    |

|             | 19          | 1                | Combinational      | None                       | Pin     |

|             | 12-13       | 7-8              | Combinational      | None                       | Pin     |

| 14H4        | 14-17       | 3-6              | Combinational      | Comb/High                  | None    |

|             | 18-19       | 1-2              | Combinational      | None                       | Pin     |

|             | 12-13       | 7-8              | Combinational      | None                       | Pin     |

| 14L4        | 14-17       | 3-6              | Combinational      | Comb/Low                   | None    |

|             | 18-19       | 1-2              | Combinational      | None                       | Pin     |

|             | 12-14       | 6-8              | Combinational      | None                       | Pin     |

| 16C1        | 15          | 5                | Combinational      | Comb/Low                   | None    |

| 1001        | 16          | 4                | Combinational      | Comb/High                  | None    |

|             | 17-19       | 1-3              | Combinational      | None                       | Pin     |

|             | 12-14       | 6-8              | Combinational      | None                       | Pin     |

| 16H2        | 15-16       | 4-5              | Combinational      | Comb/High                  | None    |

|             | 17-19       | 1-3              | Combinational      | None                       | Pin     |

|             | 12-14       | 6-8              | Combinational      | None                       | Pin     |

| 16L2        | 15-16       | 4-5              | Combinational      | Comb/Low                   | None    |

|             | 17-19       | 1-3              | Combinational      | None                       | Pin     |

| 16H8        | 12          | 8                | Combinational      | Comb/High/Z                | None    |

| &           | 13-18       | 2-7              | Combinational      | Comb/High/Z                | Comb    |

| 16HD8       | 19          | 1.               | Combinational      | Comb/High/Z                | None    |

| 16L8        | 12          | 8                | Combinational      | Comb/Low/Z                 | None    |

| &           | 13-18       | 2-7              | Combinational      | Comb/Low/Z                 | Comb    |

| 16LD8       | 19          | 1                | Combinational      | Comb/Low/Z                 | None    |

|             | 12-13       | 7-8              | Combinational      | Comb/Low/Z                 | Comb    |

| 16R4        | 14-17       | 3-6              | Registered         | Reg/Low/Z                  | Reg     |

|             | 18-19       | 1-2              | Combinational      | Comb/Low/Z                 | Comb    |

|             | 12          | 8                | Combinational      | Comb/Low/Z                 | Comb    |

| 16R6        | 13-18       | 2-7              | Registered         | Reg/Low/Z                  | Reg     |

|             | 19          | 1                | Combinational      | Comb/Low/Z                 | -       |

| 16R8        | 12-19       | 1-8              | Registered         |                            | Comb    |

|             | 12          | 8                | Combinational      | Reg/Low/Z<br>Comb/Option/Z | Reg     |

| 16P8        | 13-18       | 2-7              | Combinational      | 1 ' 1                      | None    |

|             | 19          | 1                | Combinational      | Comb/Option/Z              | Comb    |

|             | 12-13       | 7-8              | Combinational      | Comb/Option/Z              | None    |

| 16RP4       | 14-17       | 3-6              |                    | Comb/Option/Z              | Comb    |

|             | 18-19       | 1-2              | Registered         | Reg/Option/Z               | Reg     |

|             | 12          | 8                | Combinational      | Comb/Option/Z              | Comb    |

| 16RP6       | 13-18       | 2-7              | Combinational      | .Comb/Option/Z             | Comb    |

| 101110      | 19          |                  | Registered         | Re/Option/Z                | Reg     |

|             | 10          | 1                | Combinational      | Comb/Option/Z              | Comb    |

# HIGH-PERFORMANCE 8-MACROCELL **ERASABLE PROGRAMMABLE LOGIC DEVICE (EPLD)**

#### TABLE 2. DEVICE SPECIFICATIONS†

| OVALDOL         | DADAMETED                     | HIGH-SPEED EPLD | HIGH-SPEED PAL SERIES 16XXB/-15 |                                                 |  |  |

|-----------------|-------------------------------|-----------------|---------------------------------|-------------------------------------------------|--|--|

| SYMBOL          | PARAMETER                     | EP330           | PAL16L8B/-15                    | PAL16R8B/-15<br>180 mA<br>N/A<br>12 ns<br>15 ns |  |  |

|                 | Supply current active         | 45 mA 180 mA    |                                 | 180 mA                                          |  |  |

| lcc             | f = 1 MHz                     | 45 MA           | TOUTHA                          | 180 mA<br>N/A<br>12 ns                          |  |  |

| t <sub>pd</sub> | Input to nonregistered output | 15 ns           | 15 ns                           | N/A                                             |  |  |

| tCO1            | Clock to output delay         | 12 ns           | 12 ns                           | 12 ns                                           |  |  |

| t <sub>su</sub> | Input setup time              | 12 ns           | 15 ns                           | 15 ns                                           |  |  |

| fmax            | Max frequency                 | 42 MHz          | 37 MHz                          | 37 MHz                                          |  |  |

<sup>†</sup> Over commercial temperature range

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (see Note 1)                          | 0.3 V to 7 V      |

|-----------------------------------------------------------------------------|-------------------|

| Instantaneous supply voltage range, V <sub>CC</sub> (t ≤ 20 ns)             | –2 V to 7 V       |

| Programming supply voltage range, VPP                                       | 0.3 V to 13.5 V   |

| Instantaneous programming supply voltage range, V <sub>PP</sub> (t ≤ 20 ns) | –2 V to 13.5 V    |

| Input voltage range, V <sub>I</sub>                                         |                   |

| Instantaneous input voltage range, V <sub>I</sub> (t ≤ 20 ns)               | –2 V to 7 V       |

| V <sub>CC</sub> or GND current range                                        | –175 mA to 175 mA |

| Operating free-air temperature, T <sub>A</sub>                              |                   |

| Storage temperature range                                                   |                   |

|                                                                             |                   |

NOTE 1: All voltage values are with respect to GND terminal.

#### recommended operating conditions

|                 |                                      | EP3  | EP330-25M            |      | EP330-25M EP330-20I  |      | 330-201              | EP330-15C |  | UNIT |

|-----------------|--------------------------------------|------|----------------------|------|----------------------|------|----------------------|-----------|--|------|

|                 |                                      | MIN  | MAX                  | MIN  | MAX                  | MIN  | MAX                  | O.VIII    |  |      |

| Vcc             | Supply voltage                       | 4.5  | 5.5                  | 4.5  | 5.5                  | 4.75 | 5.25                 | V         |  |      |

| VI              | Input voltage                        | 0    | VCC                  | 0    | Vcc                  | 0    | Vcc                  | V         |  |      |

| VIH             | High-level input voltage             | . 2  | V <sub>CC</sub> +0.3 | 2    | V <sub>CC</sub> +0.3 | 2    | V <sub>CC</sub> +0.3 | V         |  |      |

| VIL             | Low-level input voltage (see Note 2) | -0.3 | 0.8                  | -0.3 | 0.8                  | -0.3 | 0.8                  | V         |  |      |

| Vo              | Output voltage                       | 0    | Vcc                  | 0    | Vcc                  | 0    | Vcc                  | V         |  |      |

| t <sub>w</sub>  | Pulse duration, CLK high or low      | 14   |                      | 12   |                      | 10   |                      | ns        |  |      |

| t <sub>su</sub> | Setup time, input                    | 20   |                      | 16   |                      | 12   |                      | ns        |  |      |

| th              | Hold time, input                     | 0    |                      | 0    |                      | 0    |                      | ns        |  |      |

| tr              | Rise time, input                     | 3    |                      | 3    |                      | 3    |                      | ns        |  |      |

| tf              | Fall time, input                     | 3    |                      | 3    |                      | 3    |                      | ns        |  |      |

| TA              | Operating free-air temperature       | -55  | 125                  | -40  | 85                   | 0    | 70                   | °C        |  |      |

NOTE 2: The algebraic convention, in which the more negative value is designated minimum, is used in this data sheet for logic voltage levels

#### electrical characteristics over recommended ranges of supply voltage and free-air temperature (unless otherwise noted)

| PARAMETER        |                                        | TEST CONDITIONS†                     |                        |                                   | EP330-25M |      | EP330-20I |     | EP330-15C |     |      |

|------------------|----------------------------------------|--------------------------------------|------------------------|-----------------------------------|-----------|------|-----------|-----|-----------|-----|------|

|                  |                                        |                                      |                        |                                   | MIN       | MAX  | MIN       | MAX | MIN       | MAX | UNIT |

| Vон              | High-level output voltage              | V <sub>CC</sub> = MIN,               | I <sub>OH</sub> = -8   | mA                                | 2.4       |      | 2.4       |     | 2.4       |     | ٧    |

| VOL              | Low-level output voltage               | V <sub>CC</sub> = MIN,               | l <sub>OL</sub> = 24 r | nΑ                                |           | 0.5  |           | 0.5 |           | 0.5 | V    |

| 11               | Input current                          | V <sub>I</sub> = V <sub>CC</sub> max | or GND                 |                                   |           | ±10  |           | ±10 |           | ±10 | μА   |

| loz              | Off-state output current               | V <sub>CC</sub> = MAX,               | ΛO = ΛCC               | or GND                            |           | ±10  |           | ±10 |           | ±10 | μΑ   |

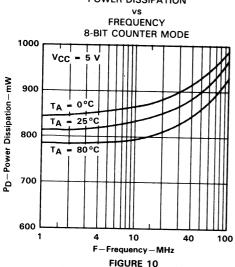

| lcc              | Supply current                         | f = 1 MHz,                           | No load,               | Programmed as<br>an 8-bit counter |           | 70   |           | 70  |           | 45  | mA   |

| Ci               | Input capacitance                      | V <sub>CC</sub> = 5 V,               | V <sub>I</sub> = 2 V,  | f = 1 MHz                         |           | . 10 |           | 10  |           | 10  | pF   |

| Co               | Output capacitance                     |                                      |                        |                                   |           | 10   |           | 10  |           | 10  | pF   |

| C <sub>clk</sub> | Clock capacitance                      |                                      |                        |                                   |           | 10   |           | 10  |           | 10  | pF   |

| Срр              | Programming input capacitance (pin 11) |                                      |                        | -                                 |           | 20   |           | 20  |           | 20  | pF   |

#### electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER‡       |                                        | TEST CONDITIONS†        |            | EP330-25M |     | EP330-20I |     | EP330-15C |     |      |

|------------------|----------------------------------------|-------------------------|------------|-----------|-----|-----------|-----|-----------|-----|------|

|                  |                                        |                         |            | MIN       | MAX | MIN       | MAX | MIN       | MAX | UNIT |

| fmax             | Maximum frequency                      |                         |            | 22        |     | 30        |     | 42        |     | MHz  |

| <sup>t</sup> pd  | Input to nonregistered output delay    | C <sub>L</sub> = 35 pF, | See Note 3 |           | 25  |           | 20  |           | 15  | ns   |

| tco              | Clock input to registered output delay | 1                       |            |           | 24  |           | 18  |           | 12  | ns   |

| tPZX             | Output enable time                     | 0 11 4                  |            |           | 20  |           | 20  |           | 15  | ns   |

| tPXZ             | Output disable time                    | See Note 4              |            |           | 20  |           | 20  |           | 15  | ns   |

| t <sub>cnt</sub> | Minimum clock period (internal)        |                         |            |           | 24  |           | 20  |           | 15  | ns   |

| fcnt             | Maximum frequency without              |                         |            | 42        |     | 50        |     | 00.0      |     |      |

|                  | feedback, (1/t <sub>cnt</sub> )        |                         |            | 42        |     | 50        |     | 66.6      |     | MHz  |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

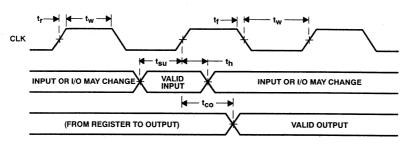

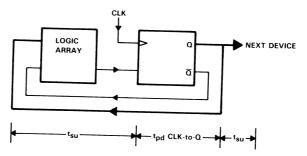

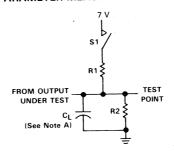

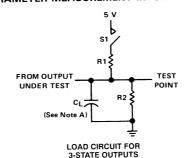

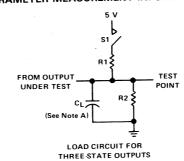

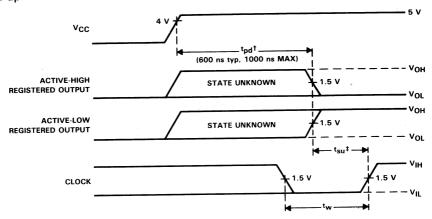

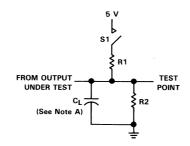

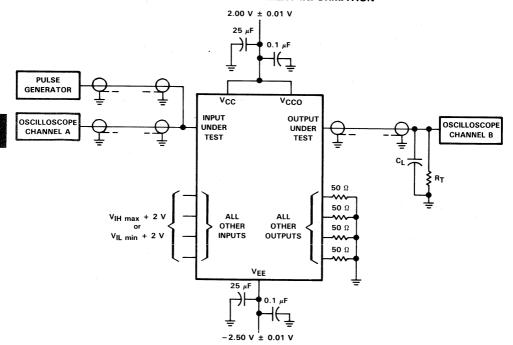

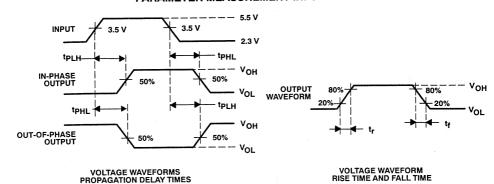

#### PARAMETER MEASUREMENT INFORMATION

#### functional testing

The EP330 is functionally tested through complete testing of each programmable EPROM bit and all internal logic elements, thus ensuring 100% programming yield. The erasable nature of the EP330 allows test program patterns to be used and then erased.

<sup>‡</sup> Letter symbols for switching characteristics and timing requirements in this data sheet have been chosen for compatibility with those used in other documentation previously prepared by another supplier for similar products. Any similarity to symbols used on other TI data sheets or to those shown in glossaries in TI data books is coincidental. The meanings may not be the same.

NOTES: 3. The f<sub>max</sub> values shown represent the highest frequency of operation without feedback in the pipeline condition.

<sup>4.</sup> This is for an output voltage change of 500 mV.

# HIGH-PERFORMANCE 8-MACROCELL ERASABLE PROGRAMMABLE LOGIC DEVICE (EPLD)

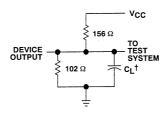

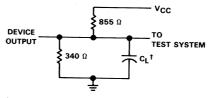

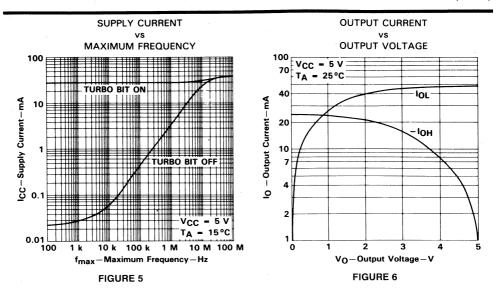

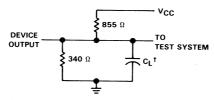

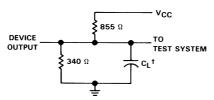

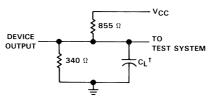

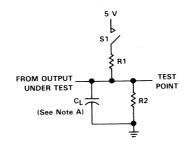

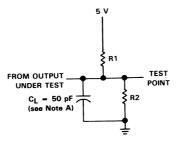

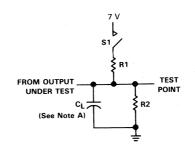

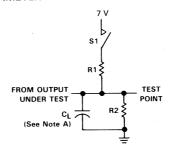

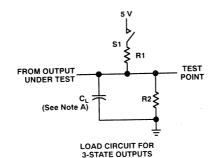

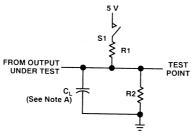

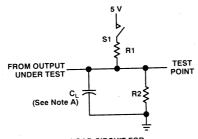

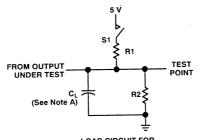

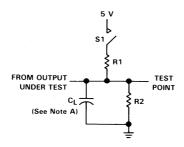

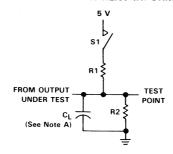

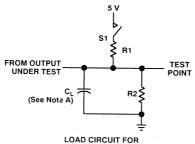

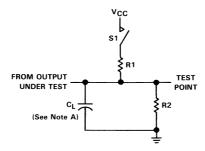

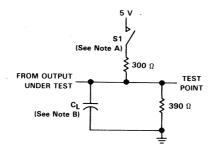

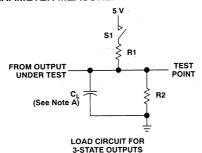

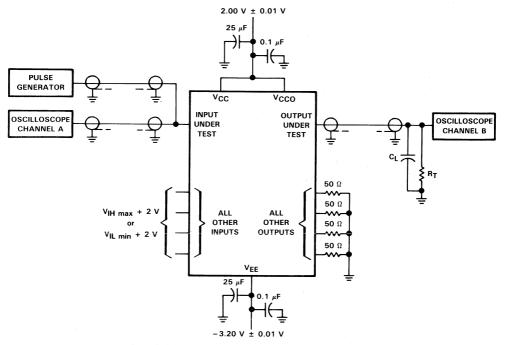

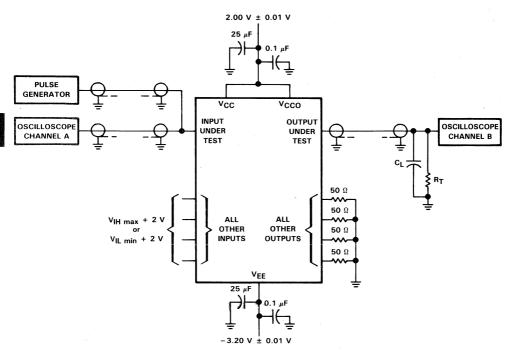

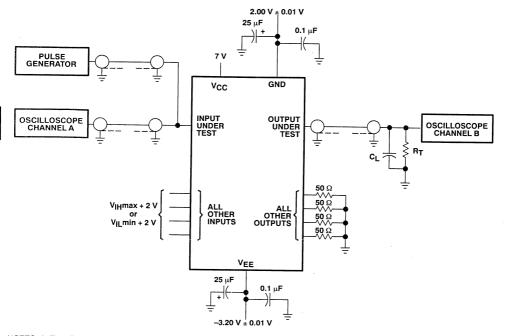

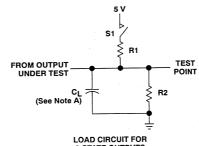

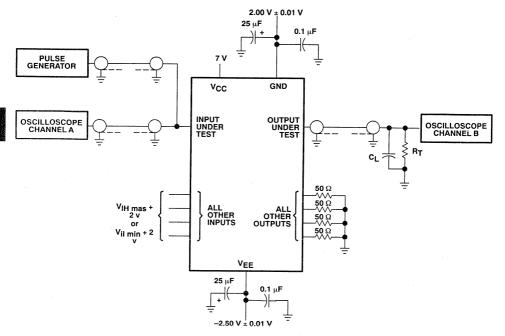

#### PARAMETER MEASUREMENT INFORMATION

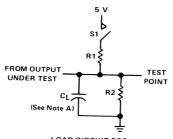

<sup>†</sup> Includes capacitance. Equivalent loads may be used for testing.

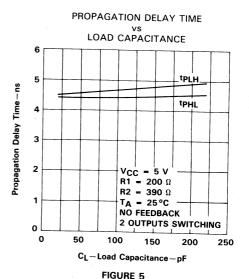

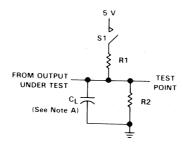

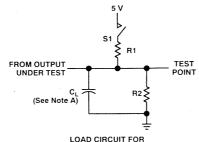

#### FIGURE 5. DYNAMIC TEST CIRCUIT

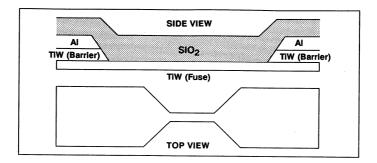

#### design security

The EP330 contains a programmable design-security feature that controls the access to the data programmed into the device. If this programmable feature is used, a proprietary design implemented in the device cannot be copied or retrieved. Therefore, a very high level of design control is achieved since programmed data within EPROM cells is invisible. The bit that controls this function, along with all other program data, may be reset by erasing the cells in the device.

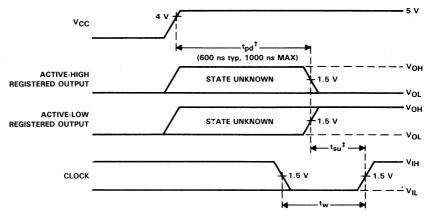

#### latchup

The EP330 input, I/O, and clock pins have been carefully designed to resist the latchup that is inherent in CMOS structures. The EP330 pins will not latch up for input voltages between -1 V and  $\text{V}_{CC} + 1 \text{ V}$  with currents up to 250 mA. During transitions, the inputs may undershoot to -2 V for periods of less than 20 ns.

Although the programming pin (pin 11) is designed to resist latchup to the 13.5-V limit, during positive-current latch-up testing, the verify mode (pin 1) and program mode (pin 11) can be inadvertently entered into, causing current flow in the pins. This should not be construed as latchup.

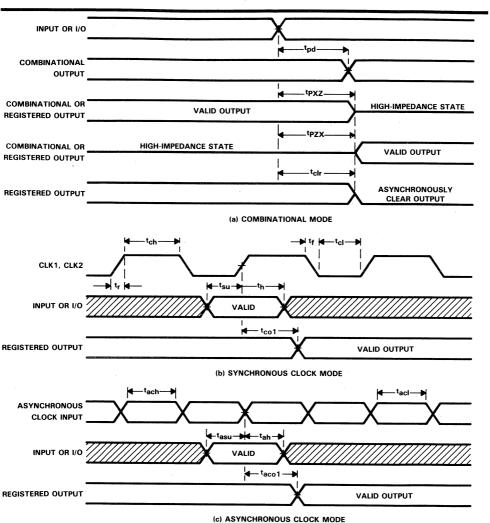

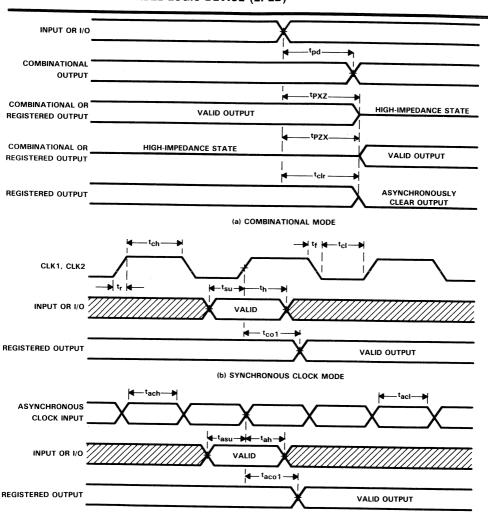

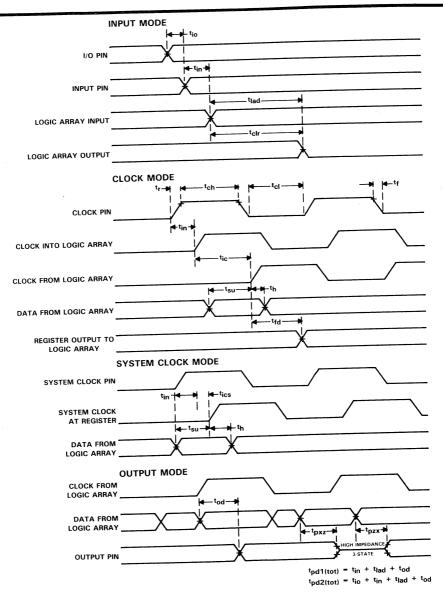

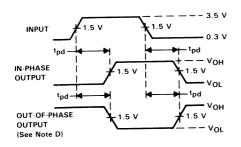

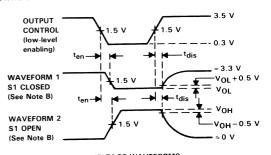

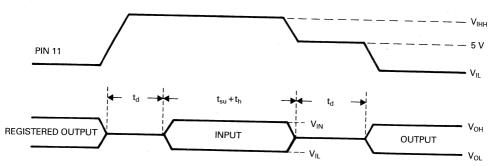

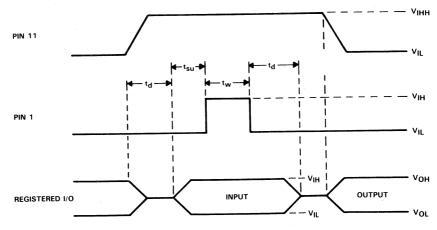

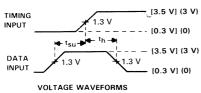

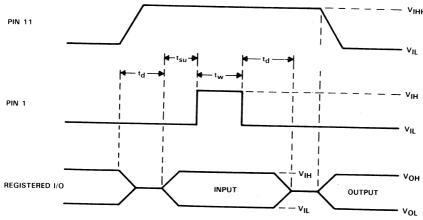

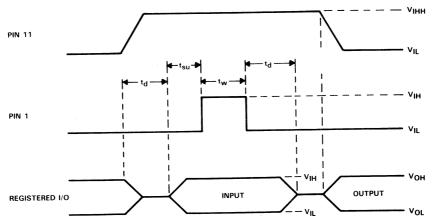

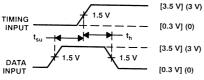

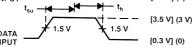

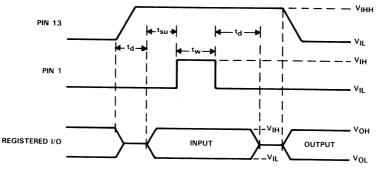

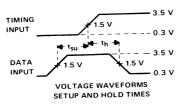

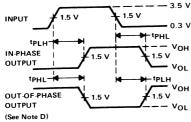

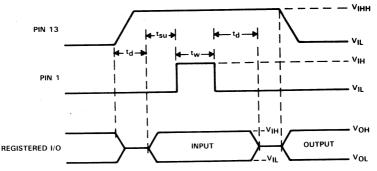

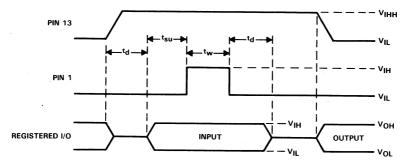

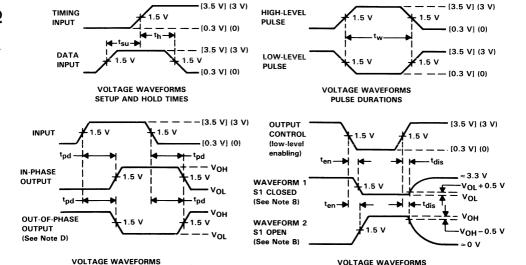

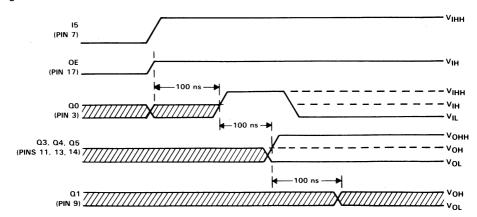

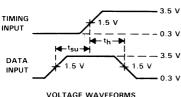

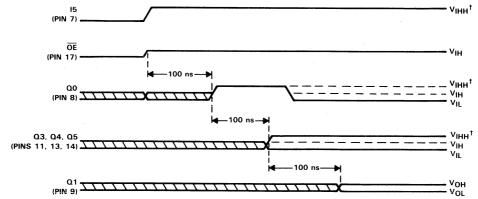

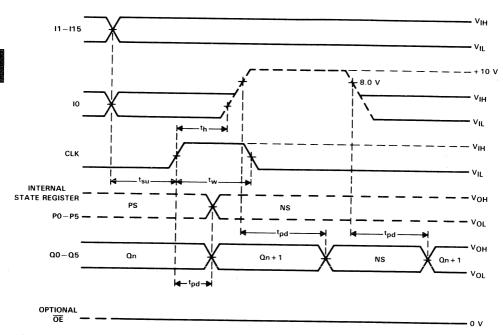

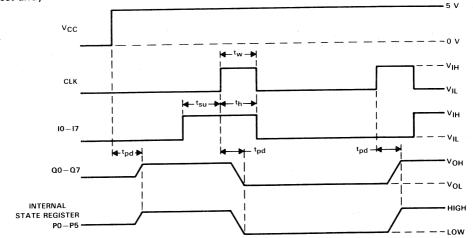

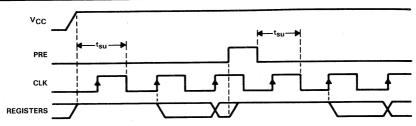

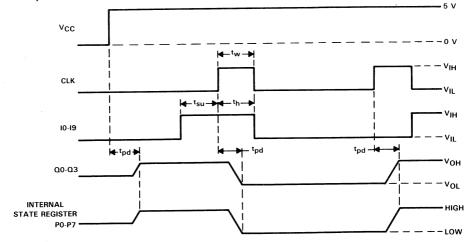

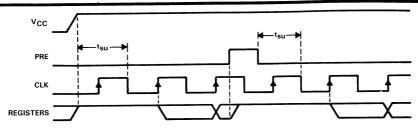

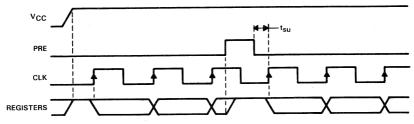

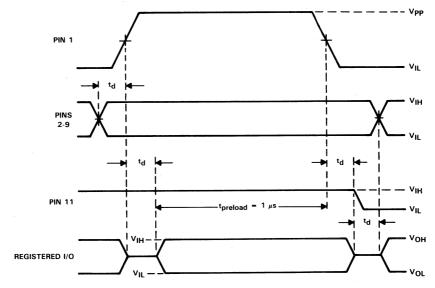

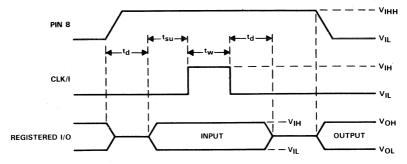

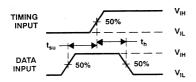

#### PARAMETER MEASUREMENT INFORMATION

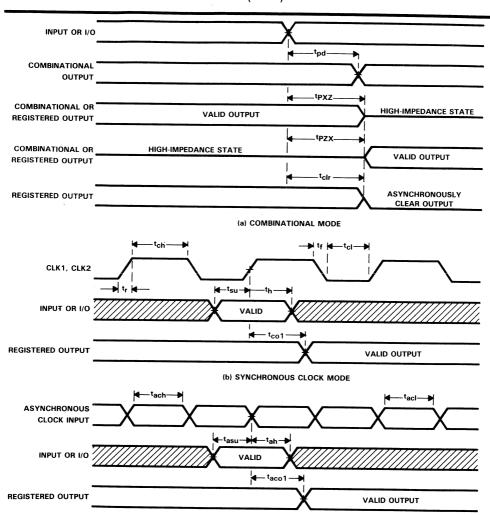

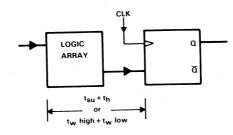

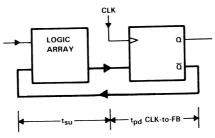

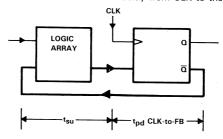

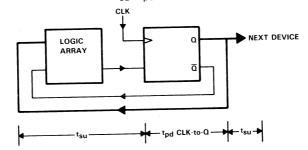

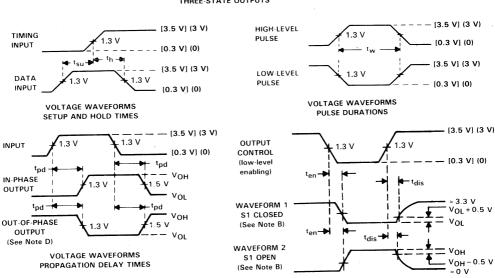

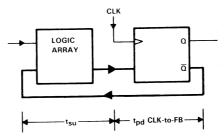

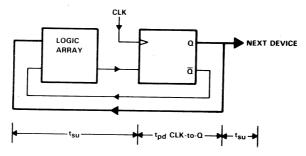

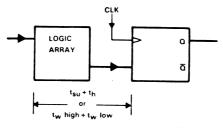

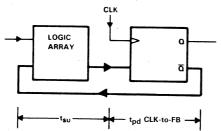

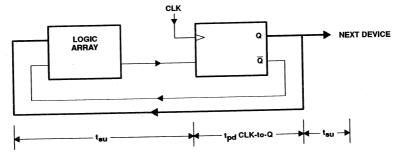

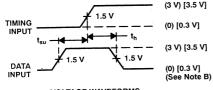

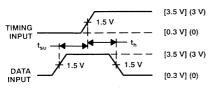

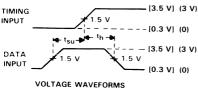

#### (a) Combinational Mode

(b) Synchronous Clock Mode

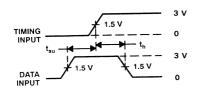

NOTES: A. Rise time (t<sub>f</sub>) and fall time (t<sub>f</sub>) < 3 ns.

- B.  $t_{\rm W}$  is measured at 0.3 V and 2.7 V. All other timing is measured at 1.5 V.

- C. Input voltage levels at 0 V and 3 V.

- D. Timing measurements are made from 2 V for a high level and 0.8 V for a low level to the 1.5 V level on the outputs.

FIGURE 6. VOLTAGE WAVEFORMS

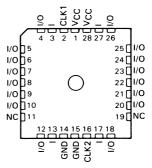

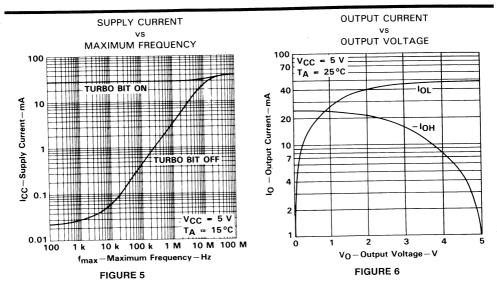

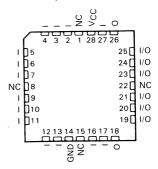

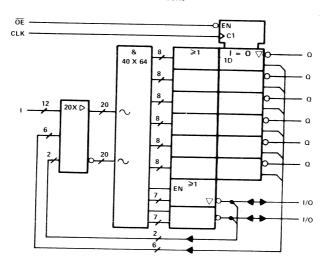

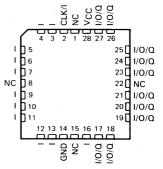

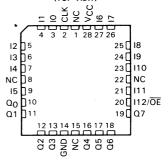

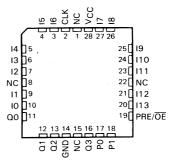

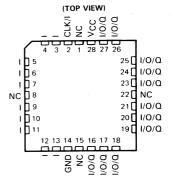

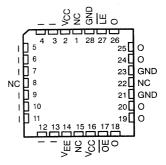

# HIGH-PERFORMANCE 16-MACROCELL ERASABLE PROGRAMMABLE LOGIC DEVICE (EPLD)

D3177, OCTOBER 1988 - AUGUST 1989

- High-Density (Over 600 Gates)

Replacement for TTL and 74HC

- Virtually Zero Standby Power . . . Typ 20 μA

- High Speed: Propagation Delay Time . . . 25 ns

- Asynchronous Clocking of All Registers or Banked Register Operation from 2 Synchronous Clocks

- Sixteen Macrocells with Configurable I/O Architecture Allowing for Up to 20 Inputs and 16 Outputs

- Each Output Macrocell User-Programmable for D, T, SR, or JK Flip-Flops with Individual Clear Control or Combinational Operation

- UV-Light-Erasable Cell Technology Allows for:

- Reconfigurable Logic

- Reprogrammable Cells

- Full Factory Testing for 100%

Programming Yields

- Programmable Design Security Bit Prevents Copying of Logic Stored in Device

- Advanced Software Support Featuring Schematic Capture, Interactive Netlist, Boolean Equations, and State Machine Design Entry

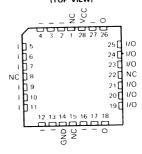

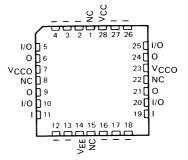

- Package Options Include Plastic [for One-Time-Programmable (OTP) Devices] and Ceramic Dual-In-Line Packages and Chip Carriers

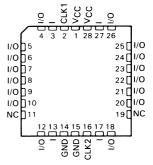

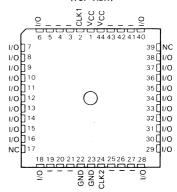

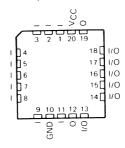

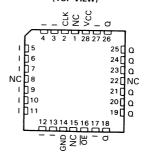

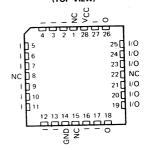

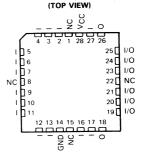

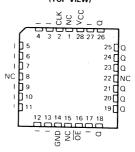

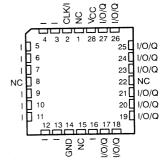

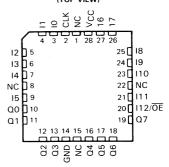

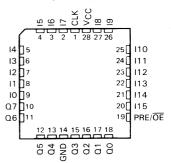

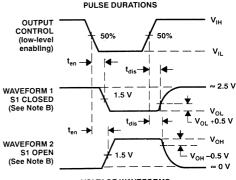

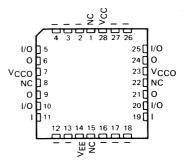

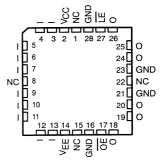

# CLK 1 U24 VCC

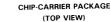

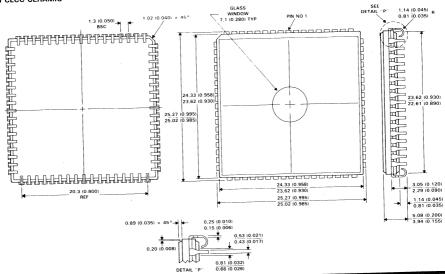

### CHIP-CARRIER PACKAGE (TOP VIEW)

NC-No internal connection

#### AVAILABLE OPTIONS

|   |            |       |                | PACKAC       | GE TYPE              | .,,          |

|---|------------|-------|----------------|--------------|----------------------|--------------|

|   | TΔ         | SPEED | CERAMIC        | CERAMIC      | PLASTIC <sup>†</sup> | PLASTIC†     |

|   | RANGE      | CLASS | DUAL-IN-LINE   | CHIP CARRIER | DUAL-IN-LINE         | CHIP CARRIER |

|   |            |       | PACKAGE (CDIP) | (CLCC)       | PACKAGE (PDIP)       | (PLCC)       |

| 1 |            | 25 ns | EP610DC-25     | EP610JC-25   | EP610PC-25           | EP610LC-25   |

|   | 0°C - 70°C | 30 ns | EP610DC-30     | EP610JC-30   | EP610PC-30           | EP610LC-30   |

|   |            | 35 ns | EP610DC-35     | EP610JC-35   | EP610PC-35           | EP610LC-35   |

<sup>†</sup> This package is for one-time-programmable (OTP) devices.

### EP610 **HIGH-PERFORMANCE 16-MACROCELL ERASABLE PROGRAMMABLE LOGIC DEVICE (EPLD)**

### description

### general

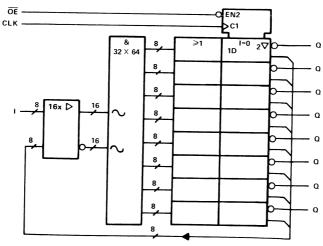

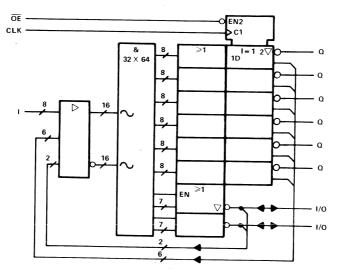

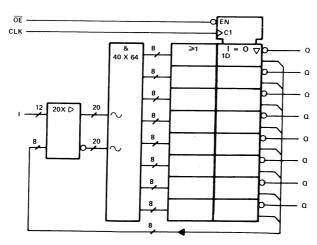

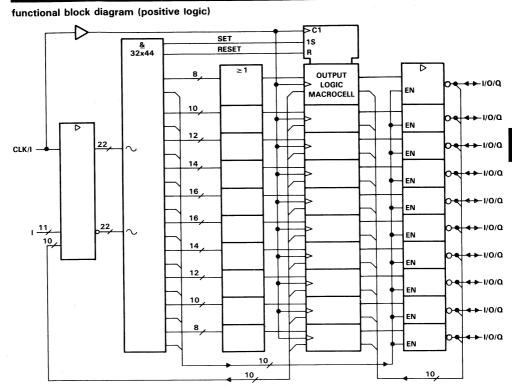

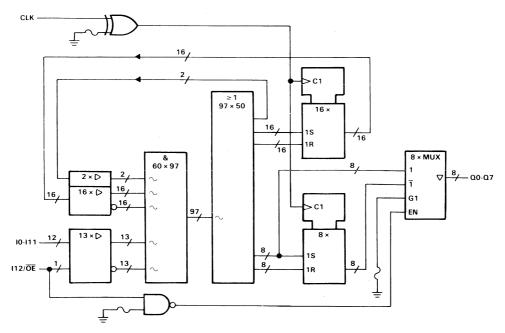

The Texas Instruments EP610 Erasable Programmable Logic Device is capable of implementing over 600 equivalent gates of SSI and MSI logic functions all in plastic and ceramic space-saving 24-pin, 300-mil dual-in-line (DIP) packages and 28-pin chip-carrier packages. It uses the familiar sum-of-products logic, providing a programmable AND with a fixed OR structure. The device accommodates both combinational and sequential (registered) logic functions with up to 20 inputs and 16 outputs. The EP610 has a user programmable output logic macrocell that allows each output to be configured as a combinational or registered output and feedback signals active high or active low.

A unique feature of the EP610 is the ability to program D, T, SR, or JK flip-flop operation individually for each output without sacrificing product terms. In addition, each register can be individually clocked from any of the input or feedback paths available in the AND array. These features allow a variety of logic functions to be simultaneously implemented.

The CMOS EPROM technology reduces the power consumption to less than 20% of equivalent bipolar devices without sacrificing speed performance. Erasable EPROM bits allow for enhanced factory testing. Design changes can be easily implemented by erasing the device with ultraviolet (UV) light.

Programming the EP610 is accomplished by using the TI EPLD Development System, which supports four different design entry methods. When the design has been entered, the software performs automatic translation into logical equations, Boolean minimization, and design fitting directly into an EPLD.

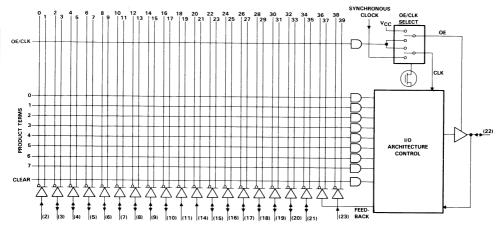

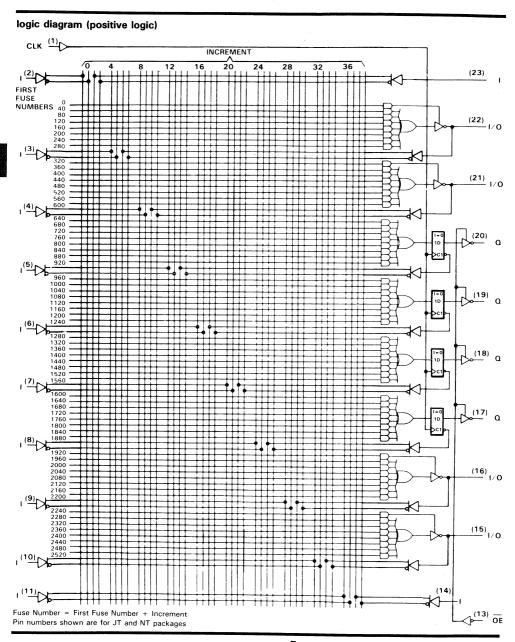

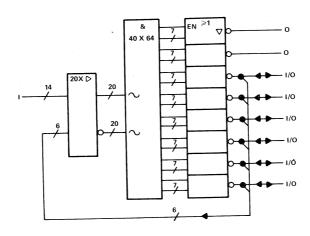

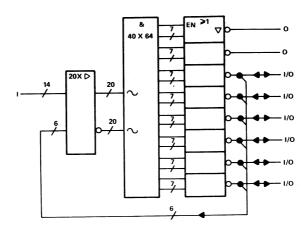

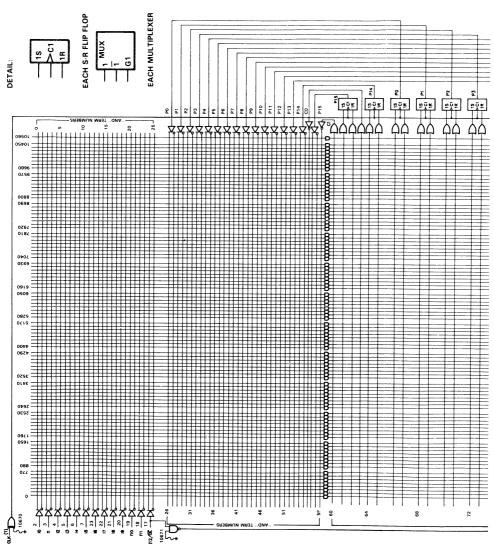

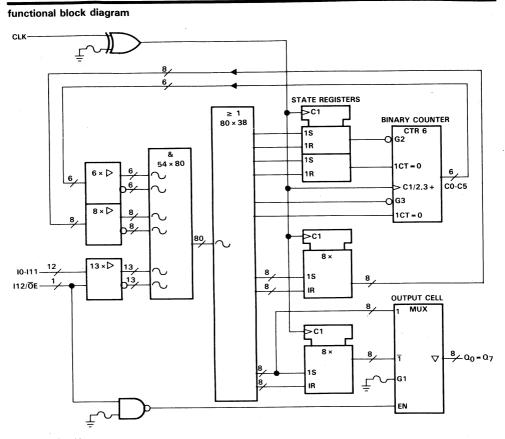

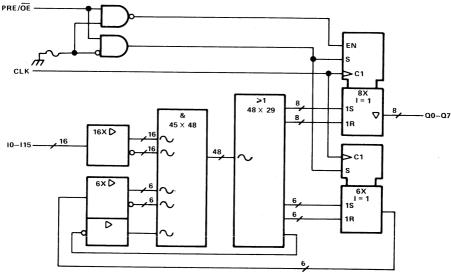

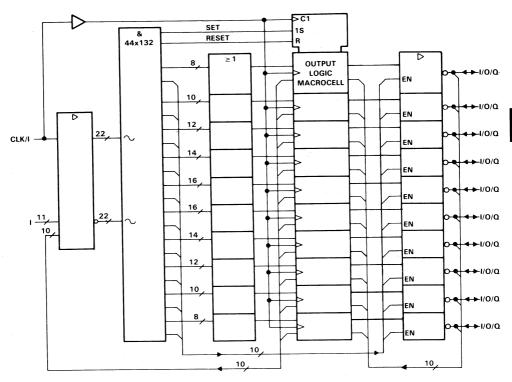

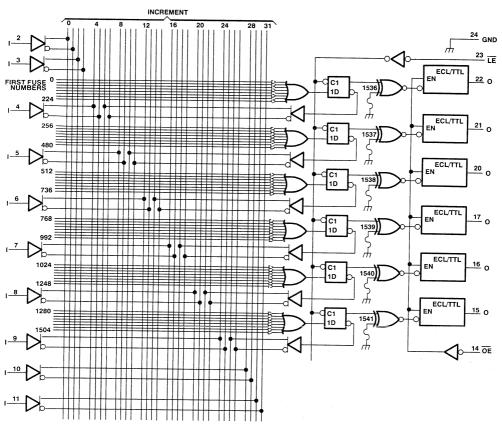

### functional

The EP610 is an Erasable Programmable Logic Device (EPLD) that uses a CMOS EPROM technology to implement logic designs in a programmable AND logic array. The device contains a revolutionary programmable I/O architecture that provides advanced functional capability for user programmable logic.

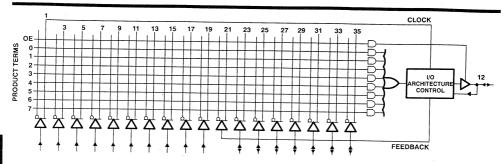

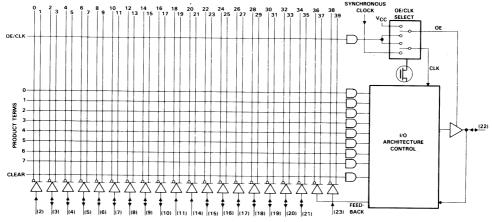

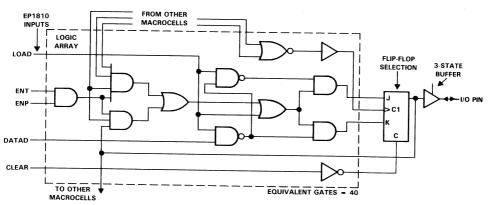

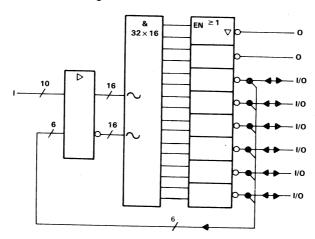

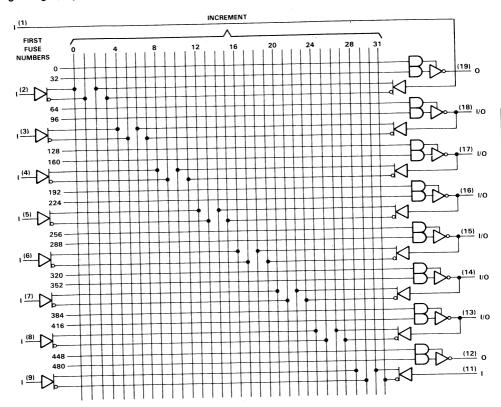

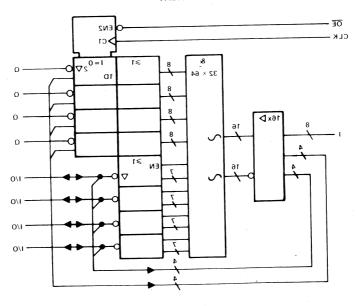

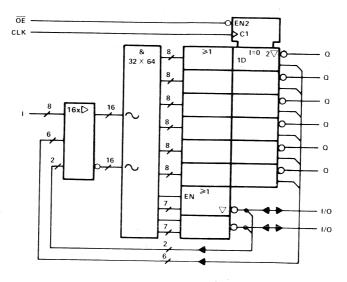

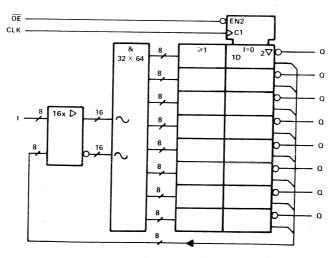

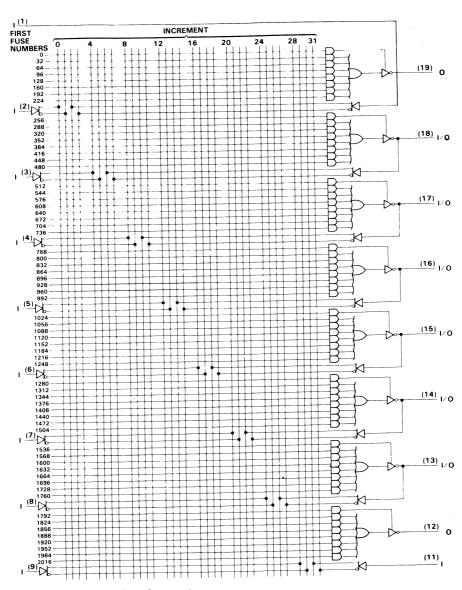

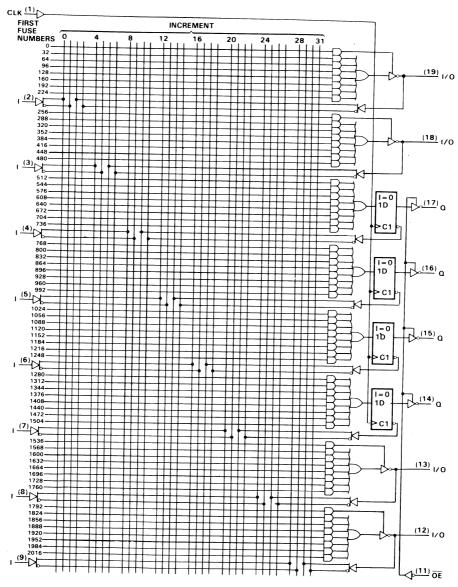

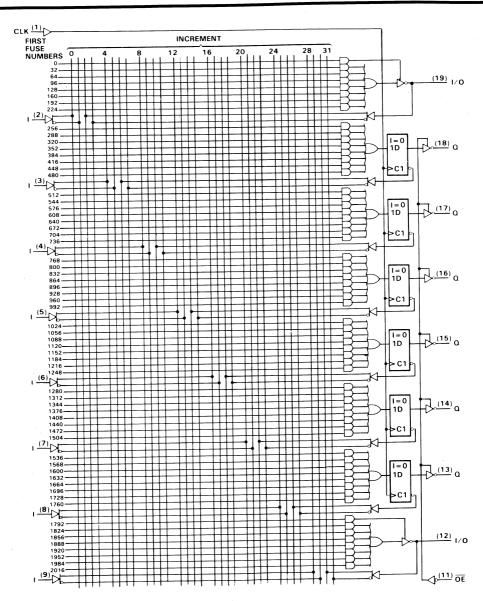

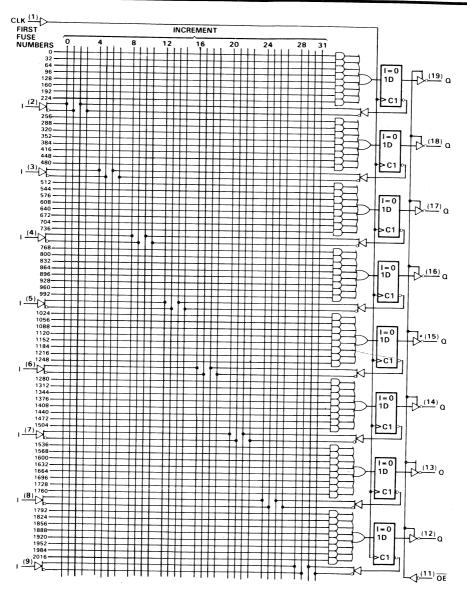

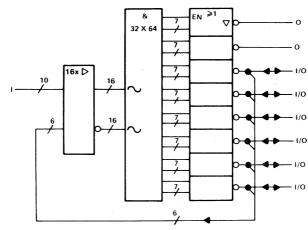

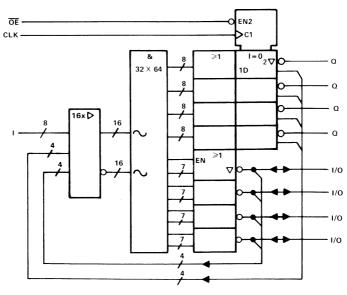

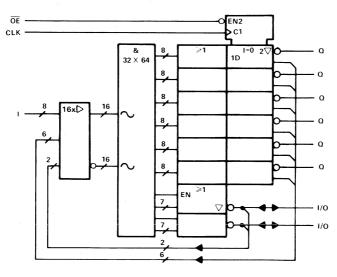

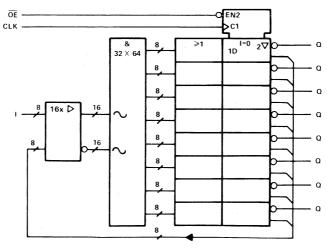

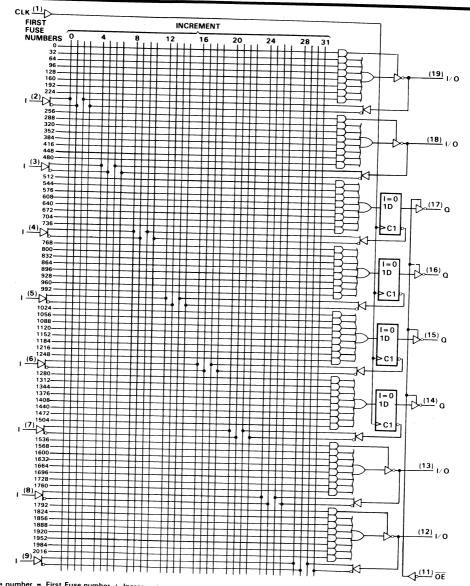

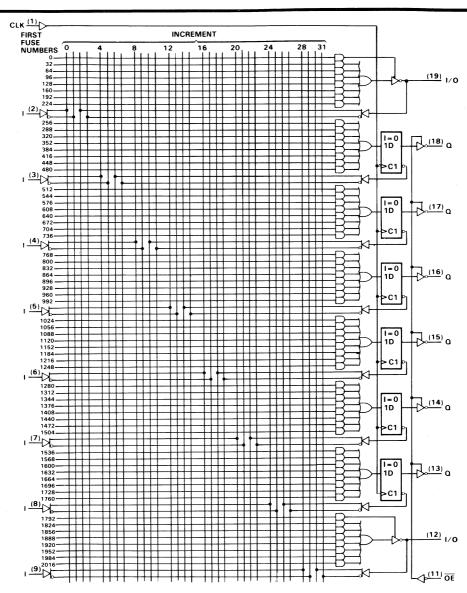

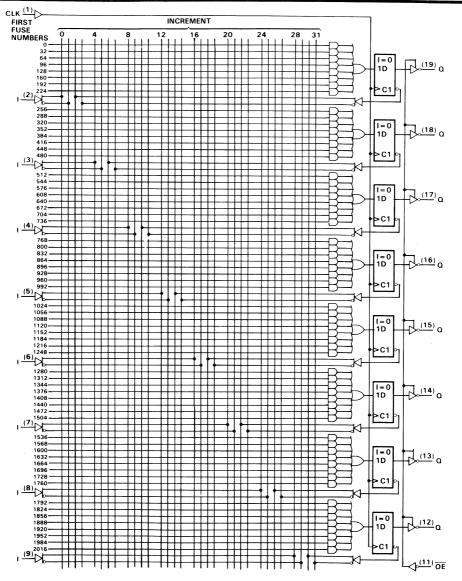

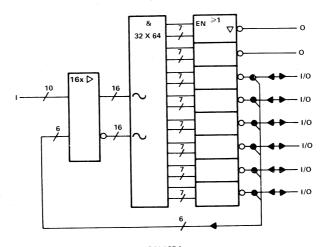

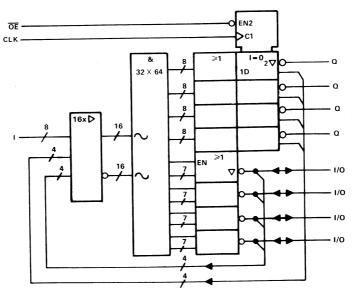

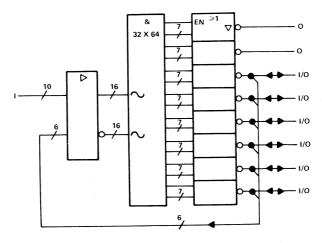

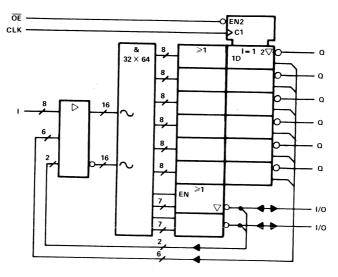

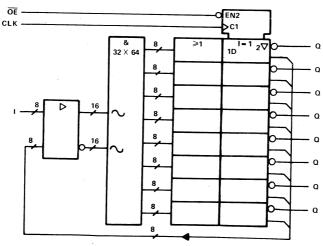

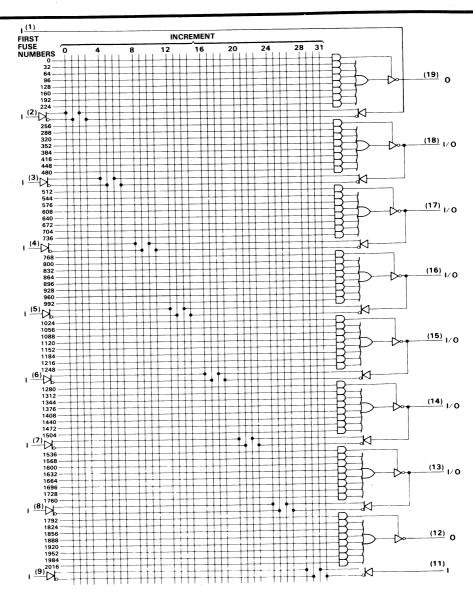

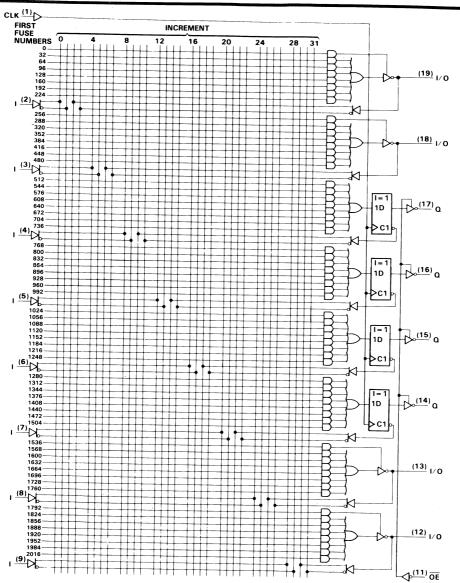

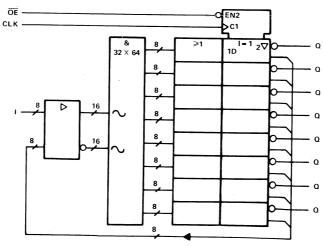

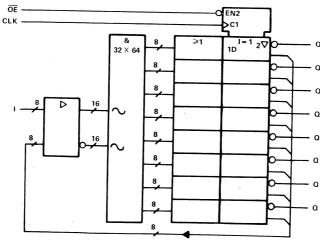

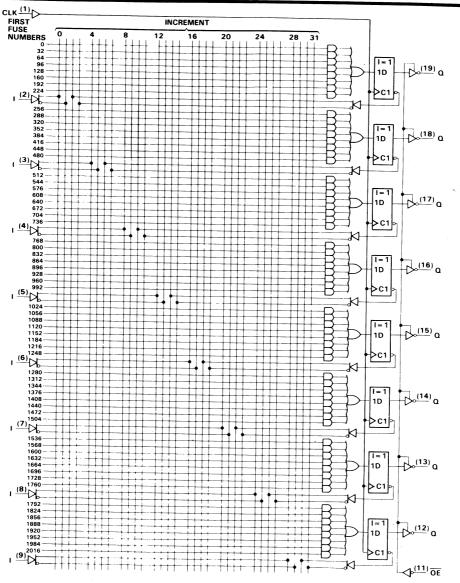

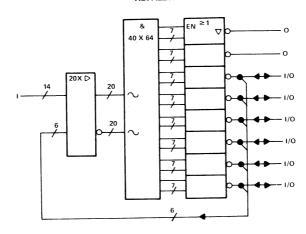

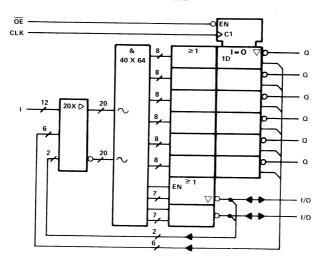

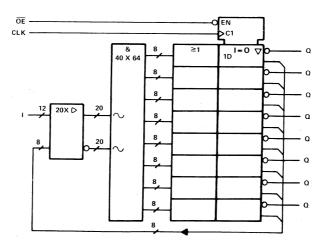

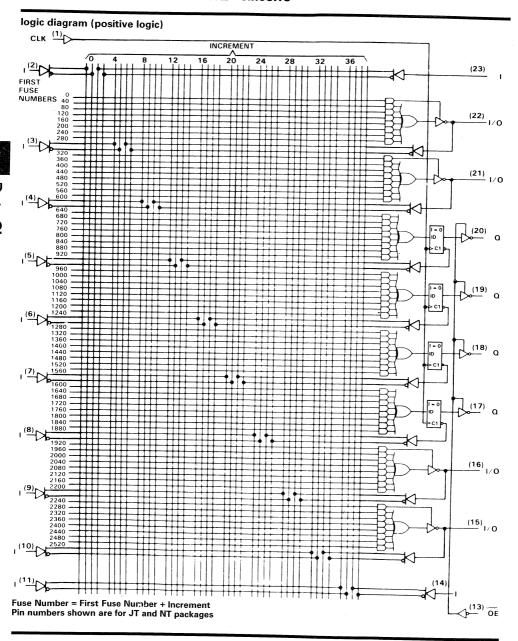

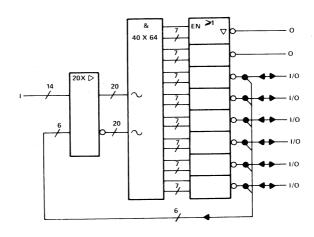

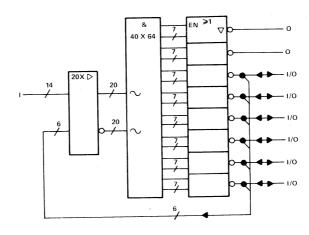

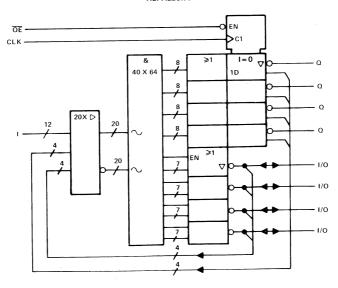

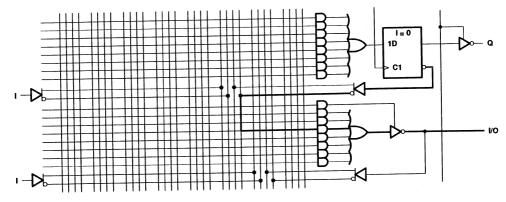

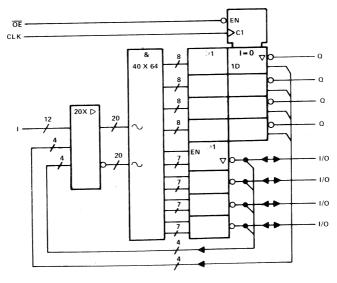

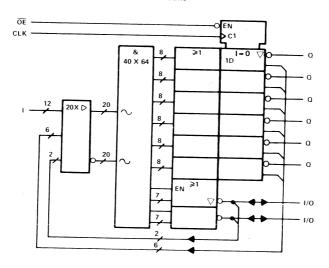

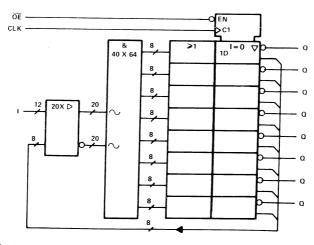

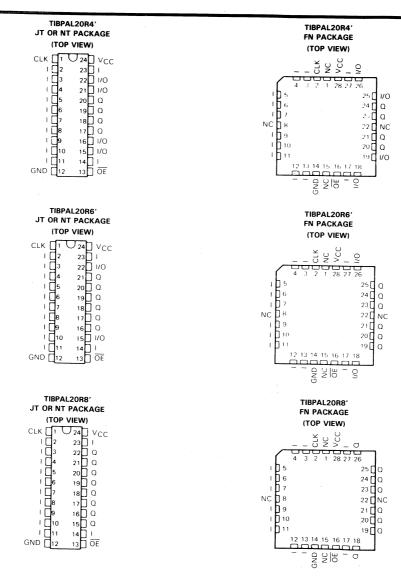

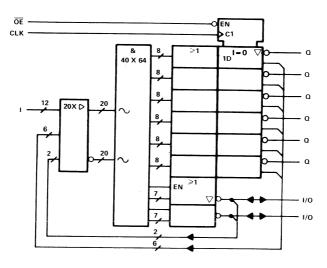

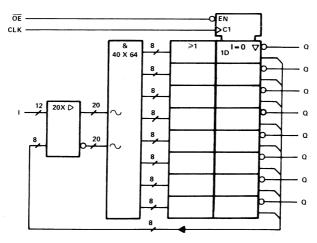

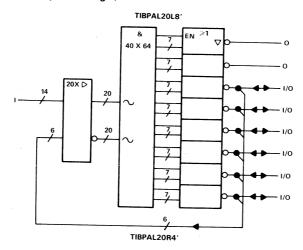

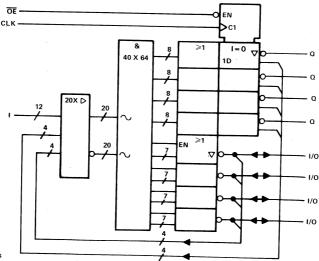

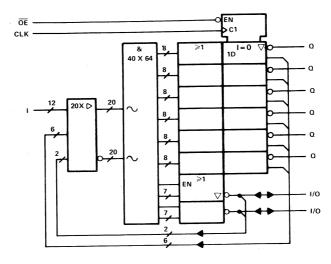

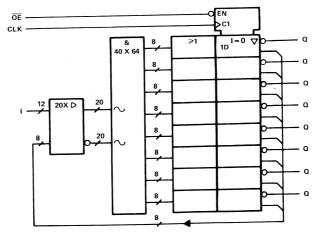

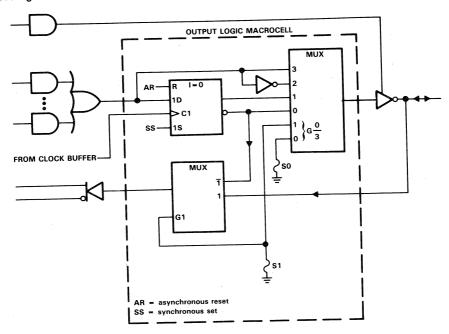

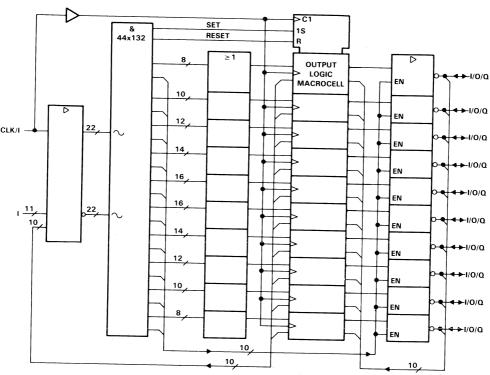

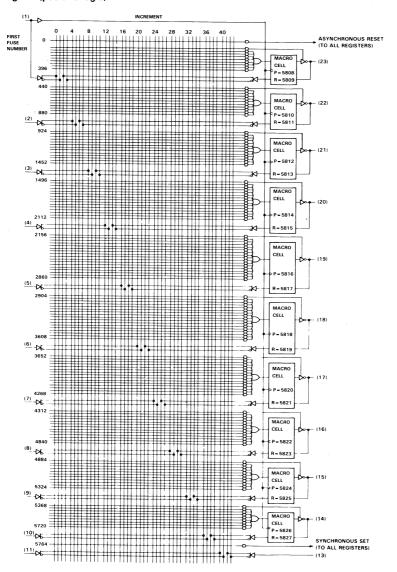

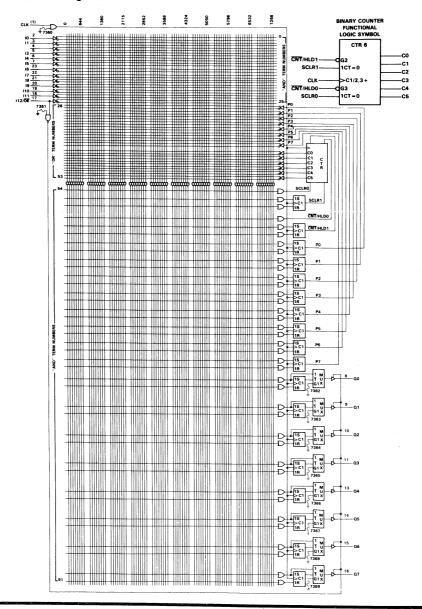

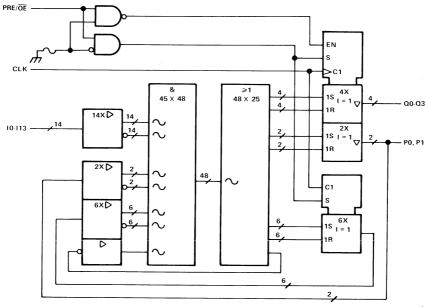

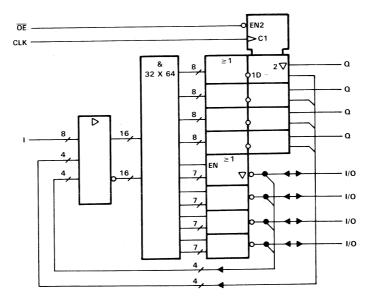

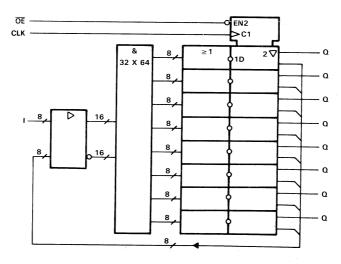

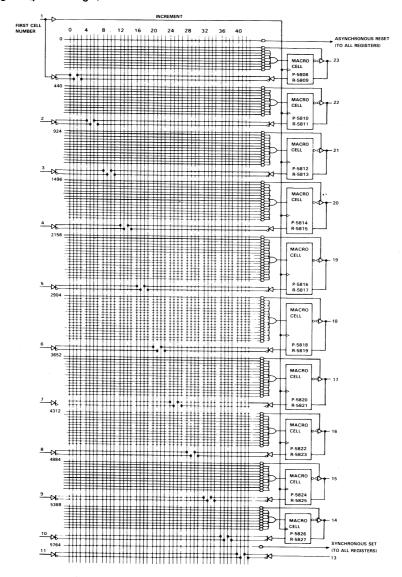

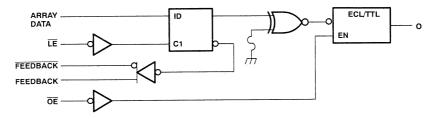

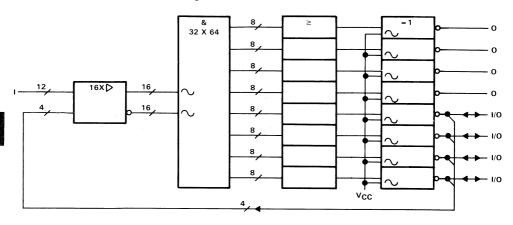

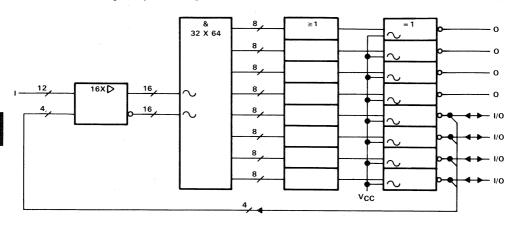

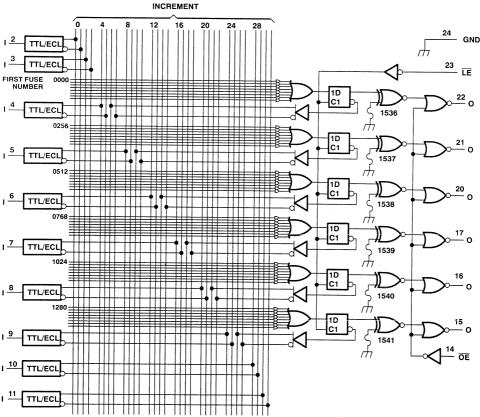

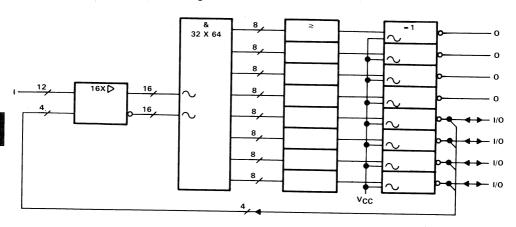

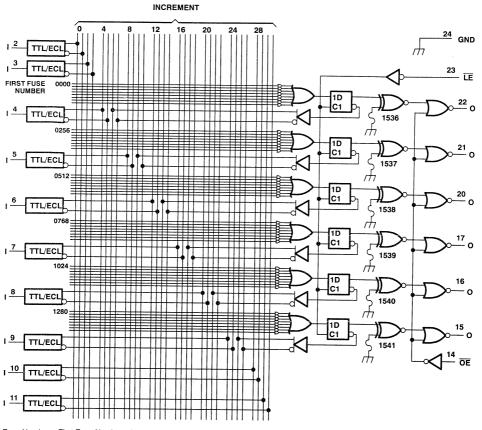

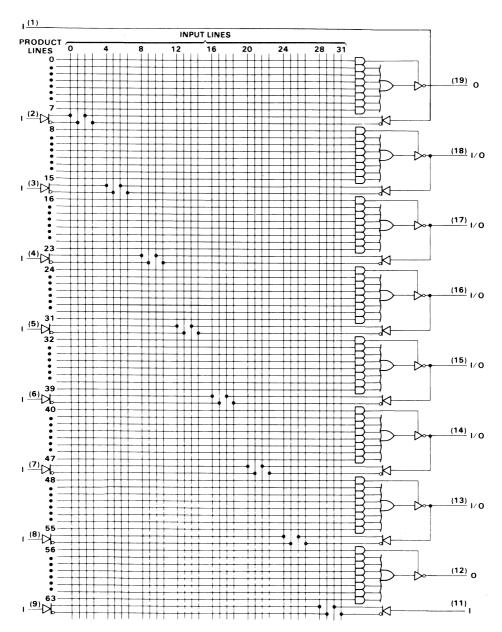

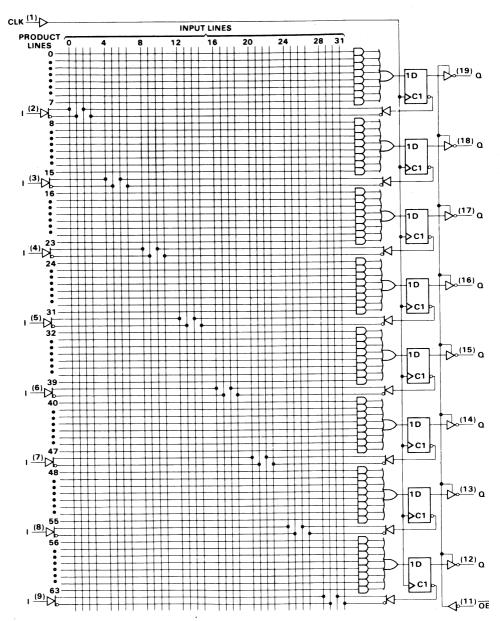

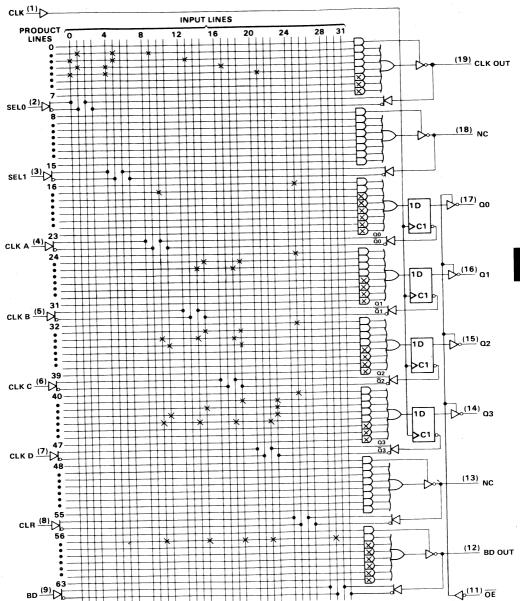

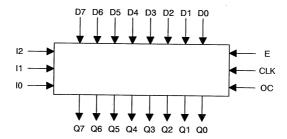

Externally, the EP610 provides 4 dedicated data inputs and 16 I/O pins, which may be configured for input, output, or bidirectional operation. Figure 1 shows the EP610 basic logic array macrocell. The internal architecture is organized with familiar sum-of-products (AND-OR) structure. Inputs to the programmable AND array come from true and complement signals from the 4 dedicated data inputs and the 16 I/O architecturecontrol blocks. The 40-input AND array encompasses 160 product terms, which are distributed among 16 available macrocells. Each EP610 product term represents a 40-input AND gate.

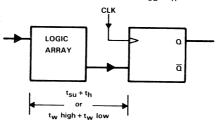

Each macrocell contains 10 product terms, 8 of which are dedicated for logic implementation. One product term is used for clear control of the macrocell internal register. The remaining product terms are used for output enable/asynchronous clock implementation.

There is an EPROM connection at the intersection point of each input signal and each product term. In the erased state, all connections are made. This means both the true and complement forms of all inputs are connected to each product term. Connections are opened during the programming process. Therefore, any product term may be connected to the true or complement form of any array input signal.

# **HIGH-PERFORMANCE 16-MACOCELL ERASABLE PROGRAMMABLE LOGIC DEVICE (EPLD)**

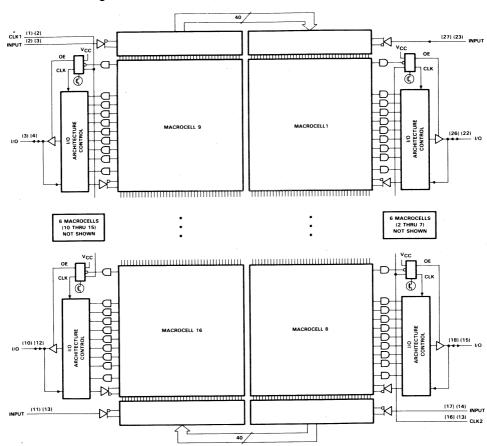

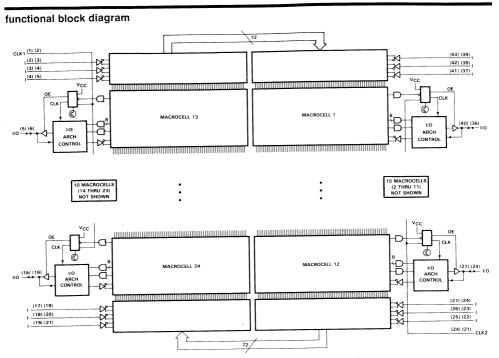

# functional block diagram CLK1 (1) [2] INPUT (2) [3] [27] (23) —— INPUT vcc Vcc CLK ₡ **(c)** I/O ARCHITECTURE CONTROL I/O ARCHITECTURE CONTROL MACROCELL1 MACROCELL S [26] (22) (3) [4] 6 MACROCELLS 6 MACROCELLS (2 THRU 7) NOT SHOWN NOT SHOWN Vcc **C** I/O ARCHITECTURE CONTROL MACROCELL 8 I/O ARCHITECTURE CONTROL MACROCELL 16 (18) (15)

Pin numbers in ( ) are for DIP packages; pin numbers in [ ] are for chip-carrier packages.

When both the true and complement forms of any signal are left intact, a logical false state results on the output of the AND gate. If both the true and complement connections are open, then a logical "don't care" applies for that input. If all inputs for the product term are programmed open, then a logical true state results on the output of the AND gate.

40

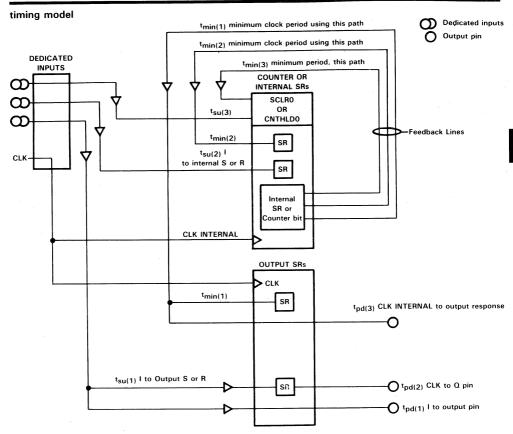

Two dedicated clock inputs provide synchronous clock signals to the EP610 internal registers. Each of the clock signals controls a bank of 8 registers. CLK1 controls registers associated with macrocells 9-16, and CLK2 controls registers associated with macrocells 1-8. The EP610 advanced I/O architecture allows the number of synchronous registers to be user defined, from one to sixteen. Both dedicated clock inputs are positive-edge triggered.

[17] (14) INPUT [16] (13) CLK2

# **HIGH-PERFORMANCE 16-MACROCELL ERASABLE PROGRAMMABLE LOGIC DEVICE (EPLD)**

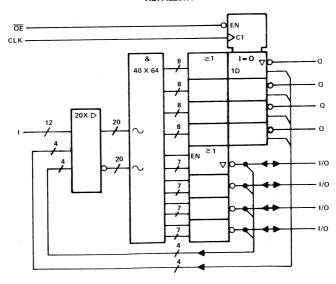

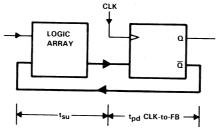

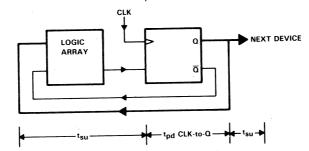

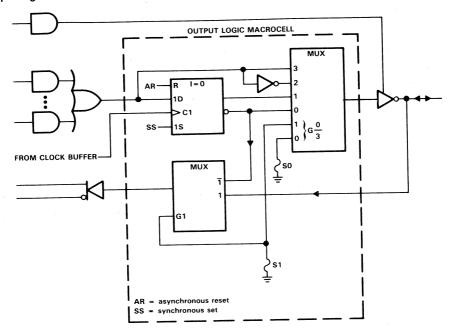

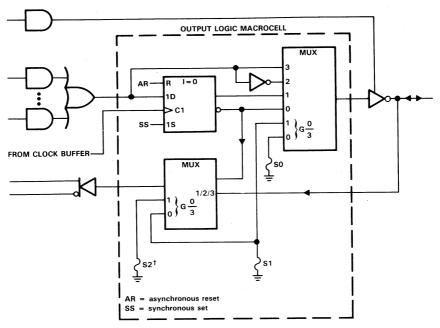

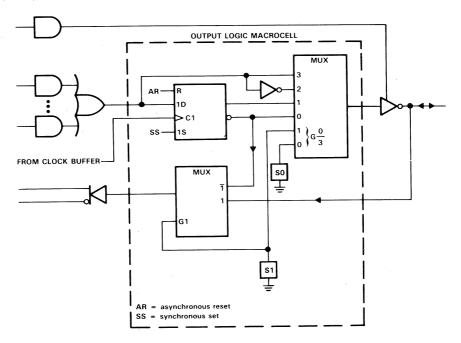

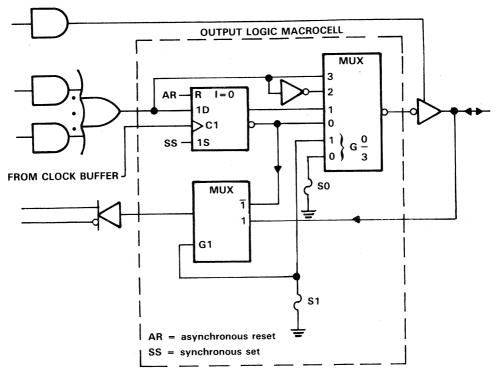

### I/O architecture

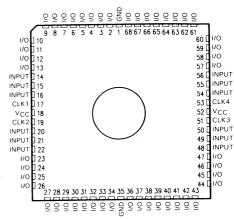

The EP610 input/output architecture provides each macrocell with over 50 possible I/O configurations. Each I/O can be configured for combinational or registered output, with programmable output polarity. Four different types of registers (D, T, JK, and SR) can be implemented into every I/O without any additional logic requirements. I/O feedback selection can also be programmed for registered or input (pin) feedback. Another benefit of the EP610 I/O architecture is its ability to individually clock each internal register from asynchronous clock signals.

Pin numbers are for dual-in-line packages

FIGURE 1. LOGIC ARRAY MACROCELL (MACROCELL 1 ILLUSTRATED)

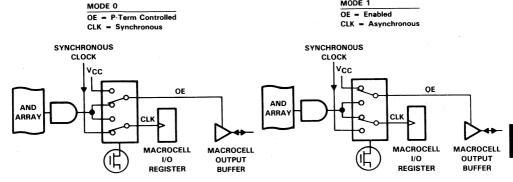

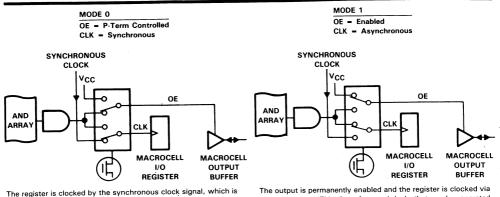

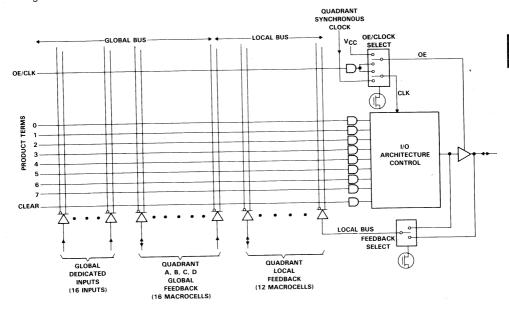

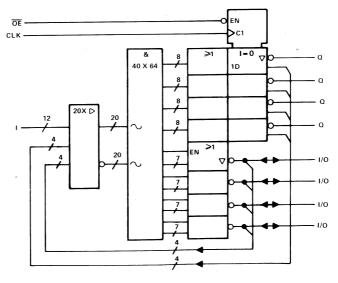

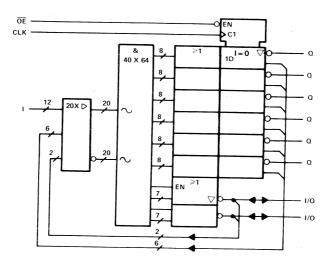

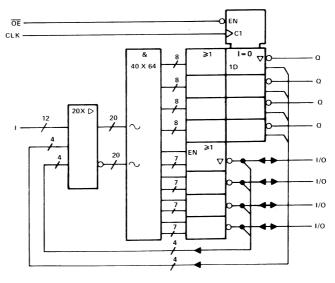

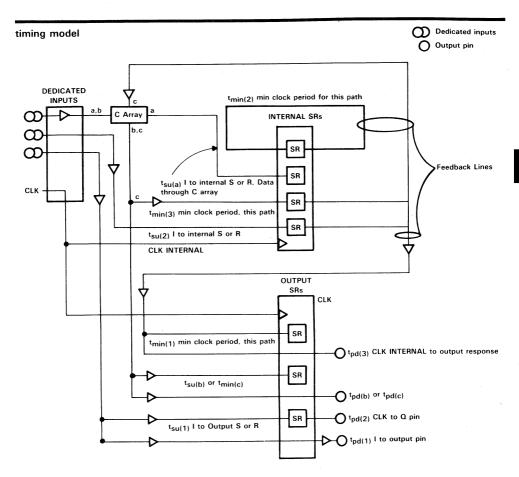

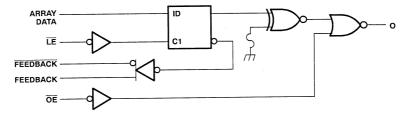

### **OE/CLK** selection

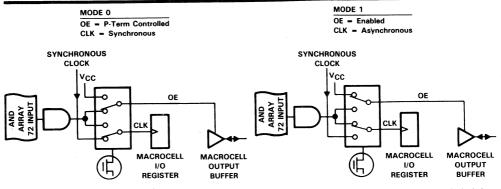

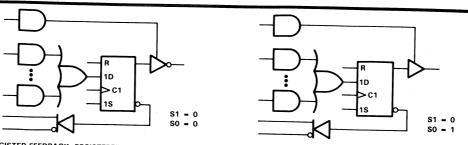

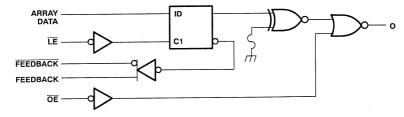

Figure 2 shows the two modes of operation that are provided by the OE/CLK select multiplexer. The operation of this multiplexer is controlled by a single EPROM bit and may be individually configured for each EP610 I/O pin. In Mode 0, the 3-state output buffer is controlled by a single product term. If the output of the AND gate is true, the output buffer is enabled. If the output of the AND gate is false, the output buffer is in the highimpedance state. In this mode, the macrocell flip-flop may be clocked by its respective synchronous clock input. After erasure, the OE/CLK select multiplexer is configured in Mode 0.

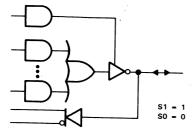

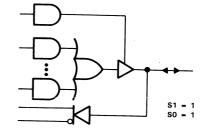

In Mode 1, the output-enable buffer is always enabled. The macrocell flip-flop may now be triggered from an asynchronous clock signal generated by the OE/CLK multiplexable product term. This mode allows individual clocking of flip-flops from any available signal in the AND array. Because both true and complement signals reside in the AND array, the flip-flop may be configured for positive- or negative-edge-triggered operation. With the clock now controlled by a product term, gated clock structures are also possible.

### **EP610** HIGH-PERFORMANCE 16-MACROCELL **ERASABLE PROGRAMMABLE LOGIC DEVICE (EPLD)**

MODE 1

The register is clocked by the synchronous clock signal, which is common to 11 other Macrocells. The output is enabled by the logic from the product term.

The output is permanently enabled and the register is clocked via the product term. This allows for gated clocks that may be generated from elsewhere in the EP610.

#### FIGURE 2. OE/CLK SELECT MULTIPLEXER

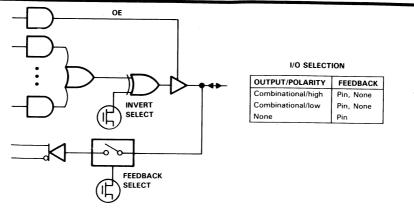

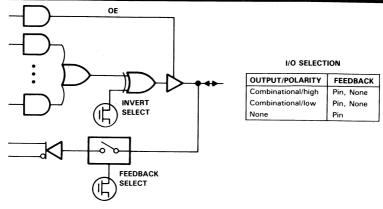

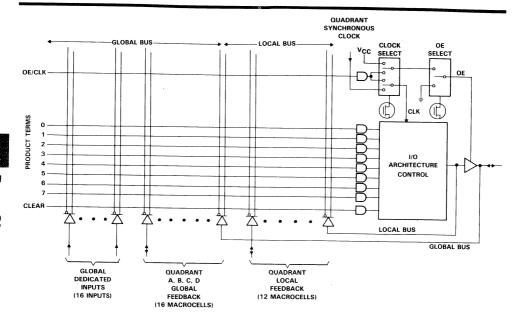

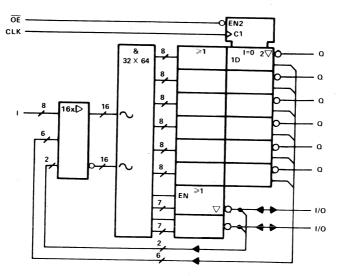

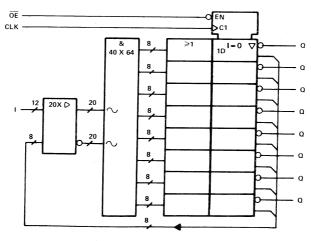

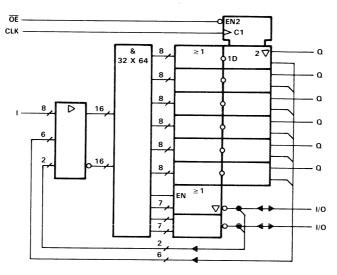

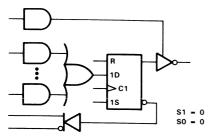

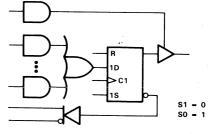

### output/feedback selection

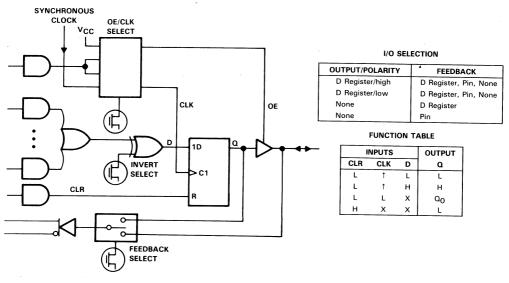

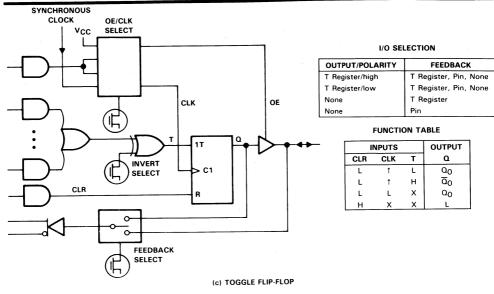

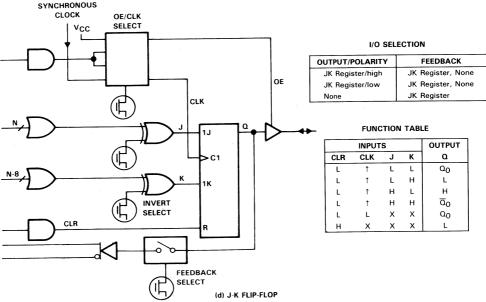

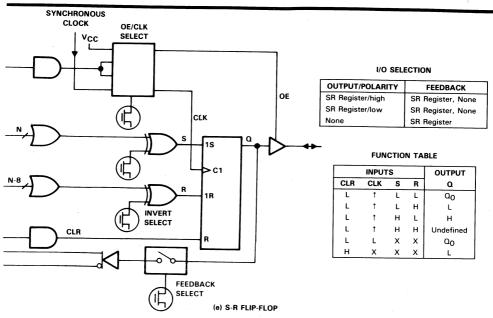

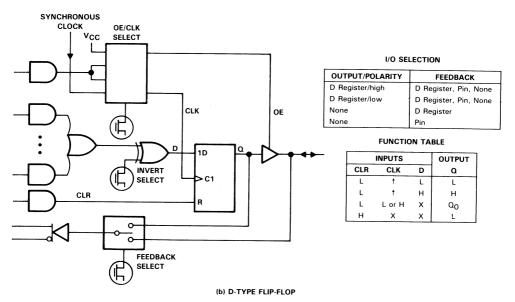

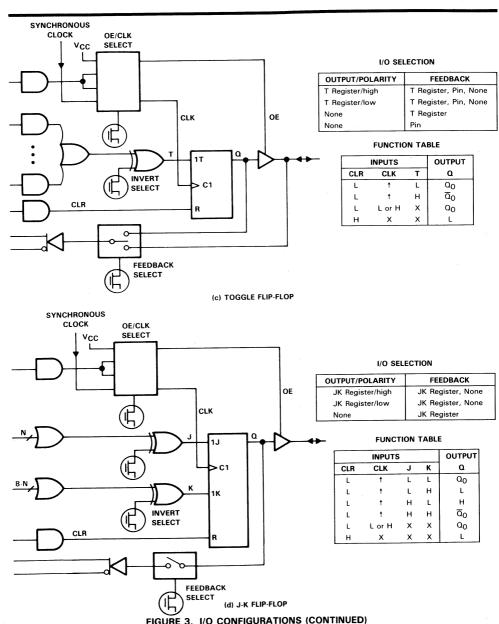

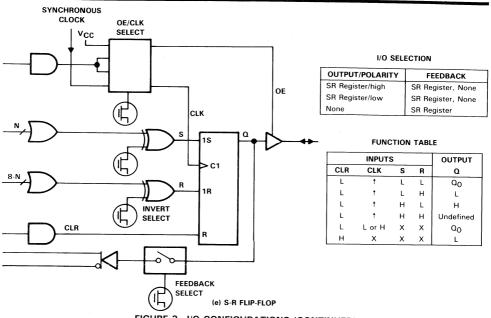

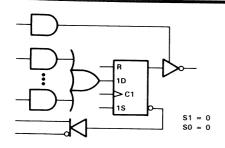

Figure 3 shows the EP610 basic output configurations. Along with combinational output, 4 register types are available. Each macrocell I/O may be independently configured. All registers have individual asynchronous clear control from a dedicated product term. When the product term is asserted, the macrocell register will immediately be loaded with a zero independently of the clock. On power-up, the EP610 performs the clear function automatically.

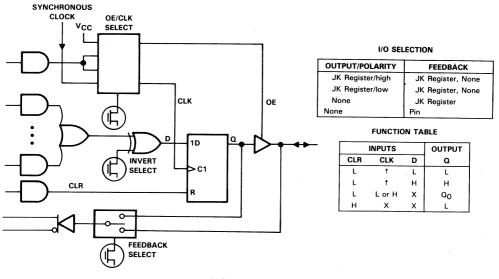

When the D or T register is selected, 8 product terms are ORed together and made available to the register input. The invert select EPROM bit determines output polarity. The feedback-select multiplexer enables register, I/O (pin), or no feedback to the AND array.

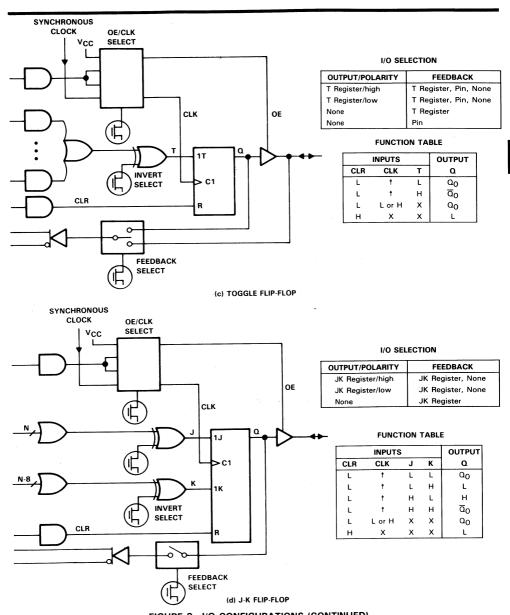

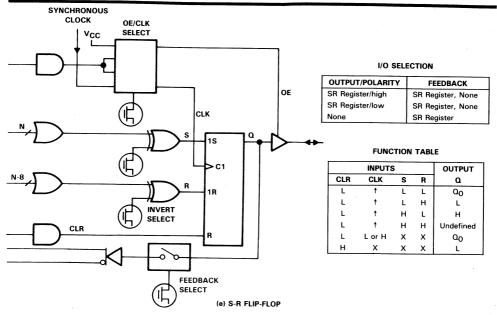

If the JK or SR registers are selected, the 8 product terms are shared between 2 OR gates. The allocation of product terms for each register input is optimized by the TI EPLD Development System. The invert select EPROM bit configures output polarity. The feedback-select multiplexer enables registered or no feedback to the AND array.

Any I/O pin may be configured as a dedicated input by selecting no output and pin feedback. No output is obtained by disabling the macrocell output buffer. In the erased state, each I/O is configured for combinational active-low output with input (pin) feedback.

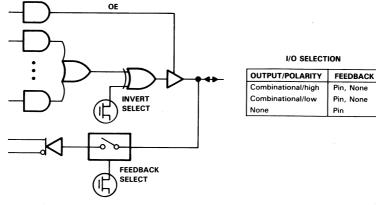

(a) COMBINATIONAL

(b) D-TYPE FLIP-FLOP

FIGURE 3. I/O CONFIGURATIONS

### **EP610 HIGH-PERFORMANCE 16-MACROCELL ERASABLE PROGRAMMABLE LOGIC DEVICE (EPLD)**

FIGURE 3. I/O CONFIGURATIONS (CONTINUED)

FIGURE 3. I/O CONFIGURATIONS (CONTINUED)

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, VCC (see Note 1) $$-0.3\text{V}$ to 7\text{V}$ Instantaneous supply voltage range, VCC (t \leq 20\text{ns}) -2\text{V}$ to 7\text{V}$ Programming supply voltage range, Vpp -0.3\text{V}$ to 13.5\text{V}$ Instantaneous programming supply voltage range, Vpp (t \leq 20\text{ns}) -2\text{V}$ to 13.5\text{V}$ Instantaneous programming supply voltage range, Vpp (t \leq 20\text{ns}) -2\text{V}$ to 13.5\text{V}$ Instantaneous programming supply voltage range, Vpp (t \leq 20\text{ns}) -2\text{V}$ to 13.5\text{V}$ Instantaneous programming supply voltage range, Vpp (t \leq 20\text{ns})$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programming supply voltage range, $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Programming supply voltage range, $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Instantaneous programming supply voltage range, Vpp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Instantaneous programming supply voltage range V (4 = 00 ==)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| instantaneous producinimila supply voltage famile, von 11 < 20 ng)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input voltage range Vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Input voltage range, VI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Instantaneous input voltage range, V <sub>I</sub> (t $\leq$ 20 ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Voc or GND ourrent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VCC or GND current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Power dissipation at 25°C free-air temperature (see Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Operating free air temporature. To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

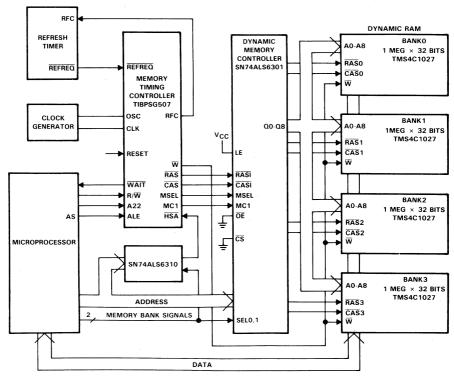

| Operating free-air temperature, T <sub>A</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |